# First Results of 0.15µm CMOS SOI Pixel Detector

Y. Arai, M. Hazumi, Y. Ikegami, T. Kohriki, O. Tajima, S. Terada, T. Tsuboyama, Y. Unno, H. Ushiroda

IPNS, High Energy Accelerator Reserach Organization (KEK), Ibaraki 305-0801, JAPAN H. Ikeda

ISAS, Japan Aerospace Exploration Agency (JAXA), Kanagawa 229-8510, JAPAN K. Hara

Institute of Pure and Applied Science, University of Tsukuba, Ibaraki 305-8571, JAPAN H. Ishino

Department of Physics, Tokyo Institute of Technology, Tokyo 152-8551, JAPAN T. Kawasaki

*Graduate School of Science and Technology, Niigata University, Niigata 950-2181, JAPAN* E. Martin, G. Varner

Department of Physics and Astronomy, University of Hawaii, Honolulu, HI 86822, USA H. Taiima

Stanford Linear Accelerator Center, Stanford, CA 94307-4349, USA

M. Ohno, K. Fukuda, H. Komatsubara, J. Ida Oki Electric Industory Co. Ltd., Tokyo 193-8550, JAPAN

We describe a new pixel detector development project using a 0.15  $\mu$ m fully-depleted CMOS SOI (Silicon-On-Insulator) technology. Additional processing steps for creating substrate implants and contacts to form sensor and electrode connections were developed for this SOI process. A diode Test Element Group and several test chips have been fabricated and evaluated. The pixel detectors are successfully operated and first images are taken. Back gate effects on the top circuits are observed and discussed.

# 1. INTRODUCTION

A monolithic pixel detector has been pursued for a long time, but has been difficult to implement due to the different silicon characteristics required for the radiation detector and for the readout electronics circuit. Recent advances in wafer bonding techniques [1] for SOI (Silicon-On-Insulator) technology enable us to use thick, high-resistivity Si and thin, low-resistivity Si on the same processed wafer.

Transistors fabricated on the SOI wafer have less parasitic capacitance compared with conventional bulk CMOS processes, enabling higher speed and lower power consumption circuits. Compared with hybrid pixel sensors [2], the SOI pixel detector does not require bump-bonding, thus a device with finer position resolution, less material and lower cost can be achieved.

SOI processes in general are known to be radiation hard and have been used in satellite instruments [3]. Furthermore, SOI is immune to latch up phenomena since each transistor is completely isolated with SiO<sub>2</sub>, and there are no parasitic PNPN structures that can lead to latch-ups. Since the active transistor is very thin (~200 nm), there is very little charge generation in it, making it less sensitive to Single Event Upsets and Transients [4]. Due to ionization radiation damage, the transistors may have larger leakage current, though this can be mitigated by proper layout, which removes the leakage path [5].

We have started an SOI pixel detector [6] development in collaboration with OKI Electric Industry Co. Ltd. in the summer of 2005. The basic technology for fabricating the pixel detector is OKI's fully-depleted 0.15µm CMOS SOI process [7]. Additional processing steps to create substrate implants and contacts were developed.

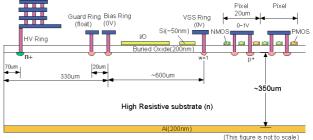

Fig. 1 illustrates a cross-section of the basic pixel detector structure we employed. Several TEG (Test Element Group) chips were designed and fabricated. Detailed structure and test results are described in the following sections for the first time.

Fig. 1. Cross-sectional view of the SOI pixel detector (n-type substrate shown).

### 2. SOI PIXEL PROCESS

The characteristics of our SOI process are summarized in Table 1. We used an SOI wafer of low resistivity ptype Si on top, and a high resistivity (>1 k $\Omega$ •cm) Si layer (called handle wafer or substrate) on the bottom. The manufacturer provides no type assignment for the handle wafer. In addition, type change could occur during processing, such as thermal donor generation by oxide contamination. Therefore we designed two kinds of TEG chips to work with p-type or n-type substrates.

Masks for the process are shared with other users (Multi Project wafer) to reduce costs. To create p+ and n+ implants and contacts, we needed additional 3 masks.

Implantation of p+/n+ to the substrate is performed after cutting the BOX layer. The implant was done at the same time as formation of the transistor drain/source region (carrier density of  $\sim 10^{20}$  cm<sup>-3</sup>) so as not to increase the number of masks and process steps.

The backside is ground mechanically from 650  $\mu$ m to 350  $\mu$ m, then plated with 200nm of aluminum. Detector voltage can be applied both from bottom and top pads, which are connected to a HV n+ implant ring.

There are 3 kinds of transistors in this SOI process; high voltage (for I/O purposes), high threshold (for normal logic), and low threshold (for high speed circuit) transistors. There are two types of body control in each transistor; floating body and body tie. High threshold transistors with body ties are used in the pixel circuit, while I/O transistors are used in the I/O buffers.

| Table 1. Featur | res of the OKI | SOI CMOS | process |

|-----------------|----------------|----------|---------|

|-----------------|----------------|----------|---------|

| Process     | 0.15µm Fully-Depleted SOI CMOS                        |  |

|-------------|-------------------------------------------------------|--|

|             | process, 1 Poly, 5 Metal layers (OKI).                |  |

| SOI wafer   | Diameter: 150 mmø                                     |  |

|             | Top Si : Cz, ~18 Ω-cm, p-type,                        |  |

|             | ~40 nm thick                                          |  |

|             | Buried Oxide: 200 nm thick                            |  |

|             | Handle wafer: Cz, >1k $\Omega$ -cm ( <i>No type</i> ) |  |

|             | assignment by supplier), 650 µm thick                 |  |

|             | (SOITEC)                                              |  |

| Backside    | Thinned to 350 µm, and plated with Al                 |  |

|             | (200 nm).                                             |  |

| p+/n+       | simultaneous with drain/source formation              |  |

| Implant     |                                                       |  |

| Supply      | Core 1V, I/O 1~1.8V                                   |  |

| Voltage     |                                                       |  |

| Transistors | High Voltage Tr (I/O), High Threshold                 |  |

|             | Tr, Low Threshold Tr.                                 |  |

|             | Floating body and body tie.                           |  |

### 2.1. Diode TEG

Prior to processing pixel TEG chips, we have fabricated diode TEG with p+/n+ implants and contacts, and measured their characteristics.

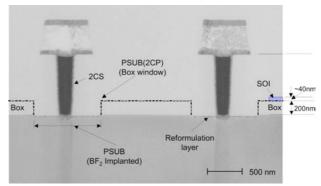

Fig. 2 shows a TEM photograph of the cross section of the p+ implant to the substrate and contact to the 1st metal layer. Sheet resistance of the p+ (n+) implant is measured to be 136 (33)  $\Omega$ /square, and the resistance of the 0.16 x 0.16  $\mu$ m<sup>2</sup> contact to the p+ (n+) implant is 218 (87)  $\Omega$ . These values agreed with expectation.

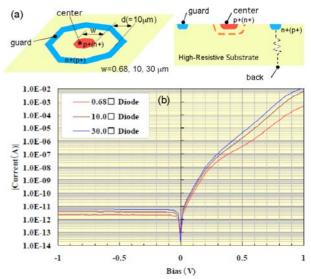

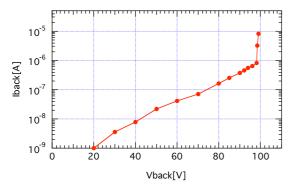

From I-V measurements of the diode TEG (Fig. 3), we determined that the substrate is n-type, and that backside wafer resistivity, measured with a 4-points probe, is about 700  $\Omega$ •cm (carrier density ~ 6 x 10<sup>12</sup> cm<sup>-3</sup>).

Fig. 2. TEM photograph of the p+ implant and contact cross section.

Fig. 3. (a) Structure of diode TEG, (b) I-V characteristics of the diode (p+ and backside) TEG for three different diode sizes.

# 3. PIXEL TEG

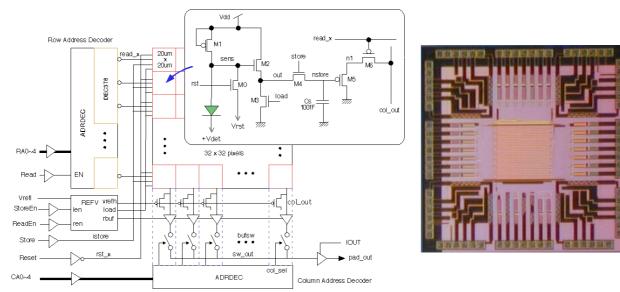

A block diagram and photograph of the pixel detector is shown in Fig. 5. Each pixel is  $20 \ \mu m$  by  $20 \ \mu m$  in size and an array of  $32 \ x \ 32$  of them are implemented. The pixel readout circuit is a standard active pixel type with a storage capacitor. At the periphery are row and column selects, control logic, and reference voltage generator circuits.

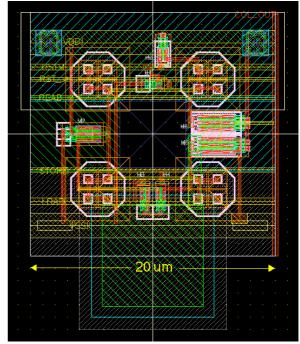

Layout of a single pixel cell is shown in Fig. 4. The center of each pixel (5.4  $\mu$ m x 5.4  $\mu$ m) is open (no metal) to allow light illumination testing. Four p+(n+) junctions are implemented in each pixel, with each junction of octagonal shape and a width of 4.4  $\mu$ m.

I-V characteristics of the detector are shown in Fig. 6. Voltage is applied from the backside Al pad. Almost the same characteristics are obtained using the HV ring pad. We could apply up to 98V without breakdown. This corresponds to about a 140 $\mu$ m depletion depth assuming the 6 x 10<sup>12</sup> cm<sup>-3</sup> carrier density. We observed the chip with an infrared camera and found hot spots in the corners of the bias ring (see Fig. 1).

Due to the back gate effect, which will be discussed in the next section, detector voltage operation is limited to a much lower value to permit electronic circuit operation.

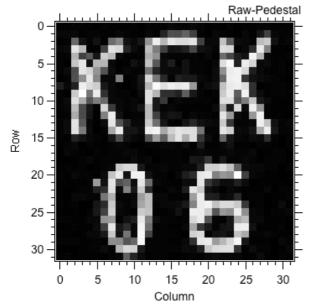

Using the pixel detector, we took images of a plastic mask placed in front of the detector by illuminating red laser light (670 nm wavelength). One such image is shown in Fig. 7. Detector bias voltage is 10V and the integration time is 7  $\mu$ s. Pedestal voltages soon after the reset are subtracted in each pixel. This reduces fixed pattern noise due to the column amplifiers. Good contrast implies good signal separation between

neighboring pixels. Collected signal in the white (saturated) part of the pixel is estimated to be about 20,000 photons from laser intensity and pixel geometry. Pixel capacitance is estimated as roughly 8 fF, so the induced voltage of the sensor node is about 400 mV. This is consistent with the observed signal amplitude.

Fig. 4. Layout of a pixel cell. Each pixel has 4 p+(n+) implants of octagonal shape. At the lower middle of the cell is the storage capacitor. The pixel center is left free of metal to allow light illumination testing.

Fig. 5. Block diagram (left) and photograph (right) of the pixel detector. Pixel size is 20 µm by 20 µm, arranged into a 32 x 32 array of pixels. Chip size is 2.5 mm by 2.5 mm.

Fig. 6. Vback - Iback characteristic of the pixel detector.

Fig. 7. An image taken by the pixel sensor with a 'KEK06' mask. Exposure time is 7  $\mu$ s, and detector bias voltage is 10V.

## 3.1. Back Gate Effect

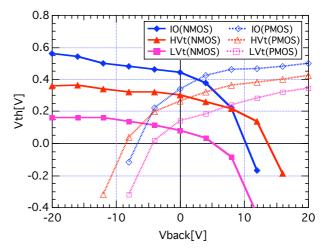

The potential under the BOX acts as a back gate of the transistors in the top Si. Threshold shifts due to this back gate voltage are plotted in Fig. 8. As the back gate voltage is increased, the threshold voltage of NMOS transistors are decreased and that of PMOS are increased. Finally the circuit stops working for excessive back gate voltage.

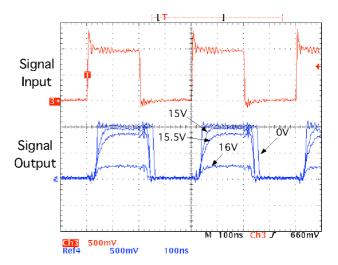

This is confirmed in the TEG chip by observing an input-output signal of the I/O buffers where the output signal from an input buffer is directly connected to the input of an output buffer. Waveforms of the input-output buffer are shown in Fig. 9. The output waveform amplitude becomes small when the back gate voltage

exceeds 15V. This is also confirmed with SPICE simulation using the threshold shifts shown in Fig. 8.

Although I/O transistors are moved 200  $\mu$ m inside of the chip (see Fig. 1), this is insufficient to avoid the back gate effect. To circumvent this back gate effect, we should place contacts to the substrate and connect them to the ground level to keep the back gate potential low enough.

Fig. 8. Measured threshold Voltage (Vth) shifts due to back gate voltage (Vback) for NMOS and PMOS transistors of the three different types available.

Fig. 9. Output signal variation due to the back gate voltage. The input buffer signal is directly connected to an output buffer in the chip. With a back gate voltage of 16V, the output signal is reduced to one fifth of its original amplitude.

### 4. SUMMARY

We have started development of a monolithic SOI pixel detector. The detector consists of a wafer-bonded sensor in high-resistivity Si mated to a CMOS circuit in low-resistivity Si. We use a commercial (OKI 0.15  $\mu$ m SOI) process with commercial wafers (SOITEC Hi-R) by adding only 3 additional masks.

Good substrate contacts and p-n junctions are confirmed. We have determined that the handle wafer is 'n' type, and has sufficient resistivity for radiation detection. Several TEG chips have been fabricated and tested. By illuminating light through a mask we successfully obtained a first image with this pixel detector.

The SOI pixel detector has many good features, such as fine segmentation, low material thickness, good radiation hardness, and low power consumption. Our results demonstrate a great potential for future high energy physics and satellite experiments.

## Acknowledgments

The authors wish to thank F. Takasaki, T. Kondo and J. Haba for their continuing support to this project. We are also grateful to Y. Sugimoto and K. Hirose for their fruitful discussions.

## Reference

- [1] SOITEC, http://www.soitec.com/.

- [2] X. Llopart et al., "Medipix2: a 64-k Pixel Readout Chip With 55-um Square Elements Working in Single Photon Counting Mode", IEEE Trans. Nucl. Sci., Vol. 49, (2002)2279-2283.

- [3] J. R. Schwank, V. Ferlet-Cavrois, M. R. Shaneyfelt, P. Paillet, and P. E. Dodd, "Radiation Effects in SOI Technologies", IEEE Trans. on Nucl. Sci., Vol. 50, (2003) 522-538.

- [4] A. Makihara et al., "Hardness-by-Design Approach for 0.15 mm Fully Depleted CMOS/SOI Digital Logic Devices With Enhanced SEU/SET Immunity", IEEE Trans. on Nucl. Sci. Vol. 52 (2005) 2524-2530.

- [5] B. W. Offord and J. S. Ruthberg, "Radiation-Hardened Silicon-on-Insulator 0.8-um Technology Design Rules", Technical Document 3065, 1999, http://www.spawar.navy.mil/sti/publications/pubs/td /3065/td3065.pdf

- [6] SOI Pixel detector R&D, http://rd.kek.jp/project/soi/

- [7] K. Morikawa and M. Mitarashi, "Low-Power LSI technology of 0.15 um FD-SOI", OKI Technical Review Issue 196, Vol. 70, No. 4, pp. 60-63, Oct. 2003. http://www.oki.com/en/otr/196/downloads/otr-196-R15.pdf