# 3D-LSI Technology for Image Sensor

Makoto Motoyoshi ZyCube

Mitsumasa Koyanagi Tohoku Univ./ZyCube

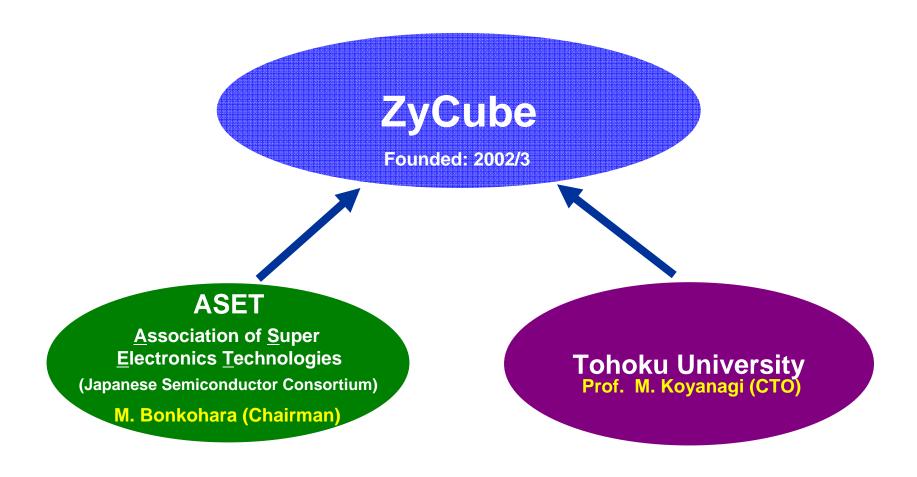

## **ZyCube History**

# **Outline**

#### 1. Introduction

- Advantages of 3D-LSI

- Potential Application

## 2. Technology Approach

- Technology breakdown

- TSV scaling, process

- Bond/Stack approaches

## 3. TSV and μ-bump

- Current technology

- **3D-LSI for Image Sensor**

- Next generation technology

#### 4. Summary

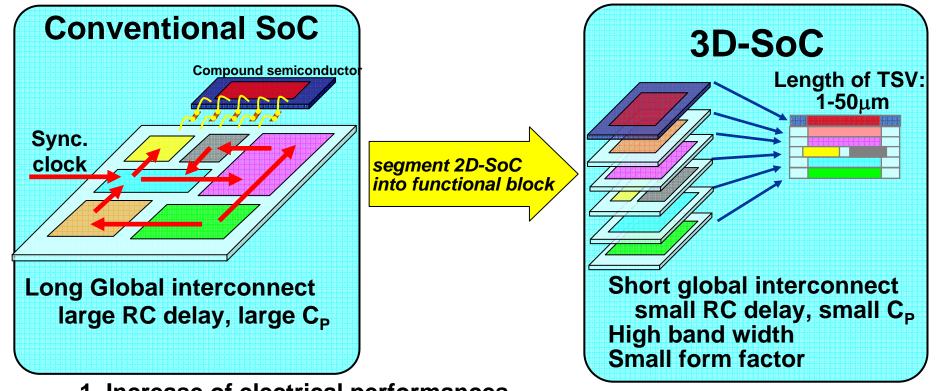

# **Advantages of 3D-LSI**

- 1. Increase of electrical performances

- 2. Increase of circuit density

- 3. New Architecture (Hyper-parallel processing, Multifunction, etc)

- 4. Heterogeneous integration

- 5. Cost reduction

- 6. Realize high performance detector with ~100% area factor in chip

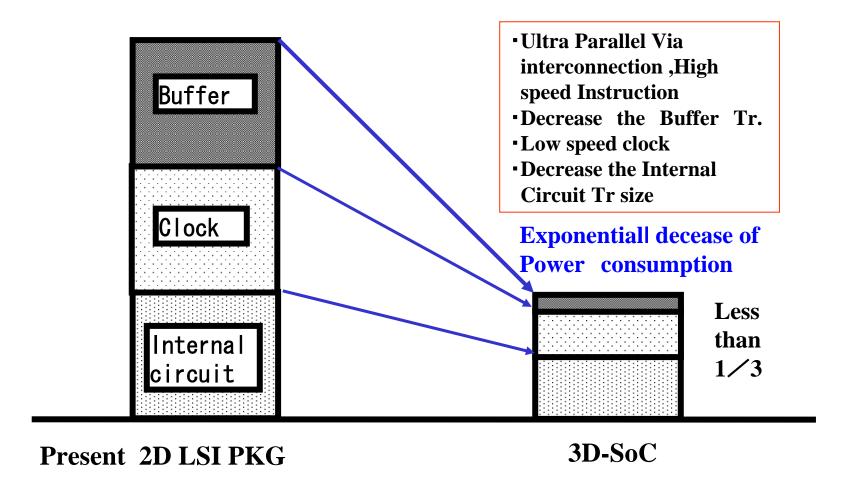

## 3D Effect for Power Consumption

#### **Estimation for MCU**

5

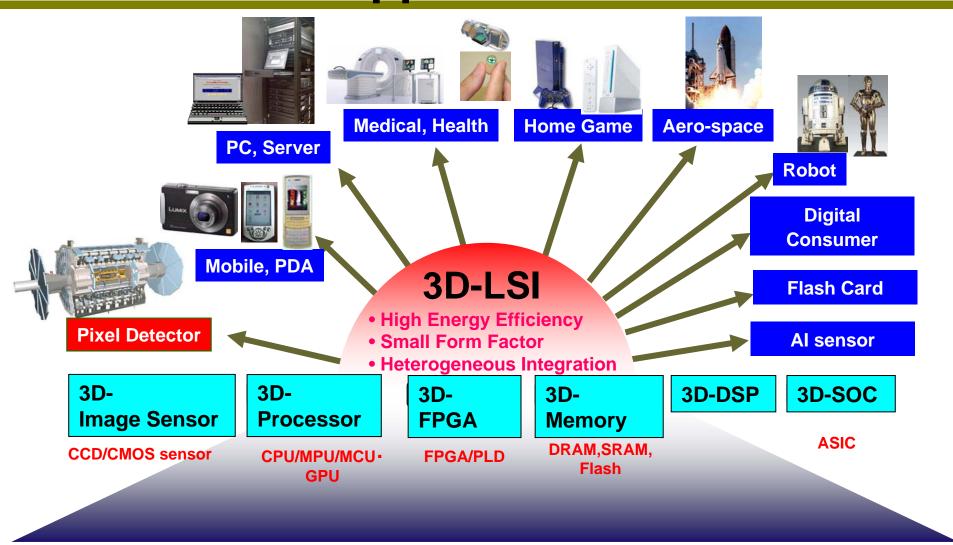

# Potential application of 3D-LSI

# **Outline**

#### 1. Introduction

- Advantages of 3D-LSI

- Potential Application

## 2. Technology Approach

- Technology breakdown

- TSV scaling, process

- Bond/Stack approaches

## 3. TSV and $\mu$ -bump

- Current technology

- **3D-LSI for Image Sensor**

- Next generation technology

8

#### 4. Summary

# **Determination of the 3D-LSI process**

## **Technology Break Down**

#### (1)Base Wafer Process

- Substrate: bulk-Si. SOI.

Compound Semiconductor, MEMS

- Thinning: Grinding, Polish, CMP,

plasma etch, wet etch

- Handling: Thin wafer Support system

#### (2)TSV formation

-Via opening: Laser drilling or DRIE

-Conductor: Cu, W, PolySi, conductive paste

-Filling method: plating, CVD, sputter, vapor deposition

-Isolation: conformal CVD, sputter,

vapor deposition

#### (3) New material

- -Adhesive (permanent/temporally)

- -Bump metal, barrier metal

- -Conductive paste

-etc

#### (5)Interposer

- -Substrate --silicon or organic?

- Embedded chips & passives?

#### (4)Stacking approach:

- Technology: Metal Thermo compression,

Direct Oxide (SiO2), Adhesive bonding...

- Integration scheme:

CoC, CoW or WoW?

Face to face or face to back?

- -Accuracy?

- -Throughput?

- -How many dies to stack?

# **Outline**

- 1. Introduction

- Advantages of 3D-LSI

- Potential Application

## 2. Technology Approach

- Technology breakdown

- TSV scaling, process

- Bond/Stack approaches

## 3. TSV and $\mu$ -bump

- Current technology

- **3D-LSI for Image Sensor**

- Next generation technology

#### 4. Summary

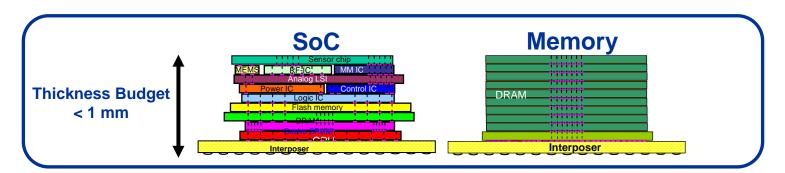

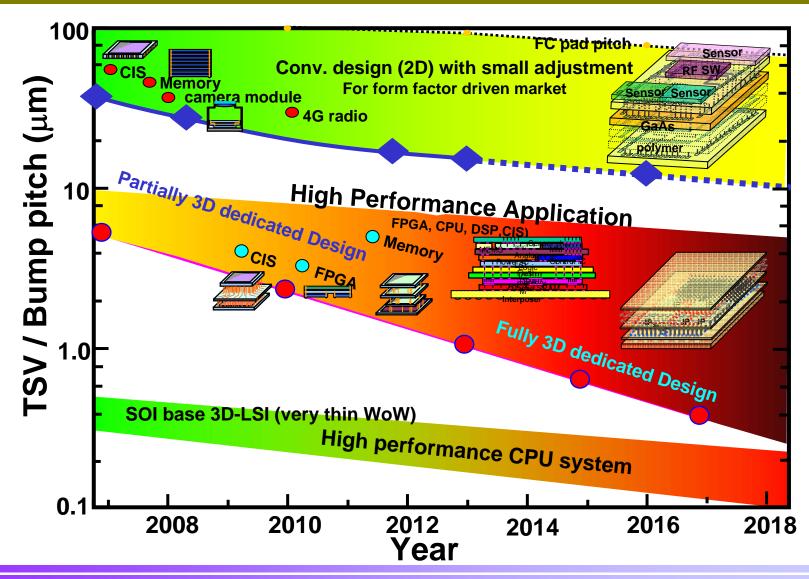

# Road Map of TSV & Bump pitch

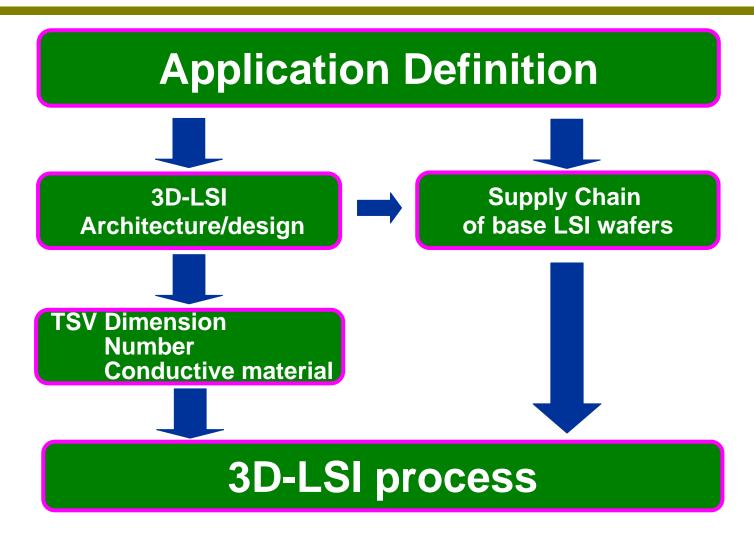

# Determination for 3D-LSI process and TSV dimension

Application SoC, Memory, Sensor, FPGA Supply Chain of base wafer

procure each wafers from one supplier or multi-supplier New design or stack conventional LSI chips

#### Main purpose of 3D-LSI

- -Performance

- -Form Factor

- -Cost reduction

- -New architecture

#### **TSV** dimension

| TSV diameter | <1um                              | ~10um 10~50um                                     | >50um                             |

|--------------|-----------------------------------|---------------------------------------------------|-----------------------------------|

| TSV depth    | <10um                             | 10~100um                                          | >100um                            |

| TSV density  | <10 <sup>6</sup> /mm <sup>2</sup> | 10 <sup>2</sup> ~10 <sup>5</sup> /mm <sup>2</sup> | <10 <sup>2</sup> /mm <sup>2</sup> |

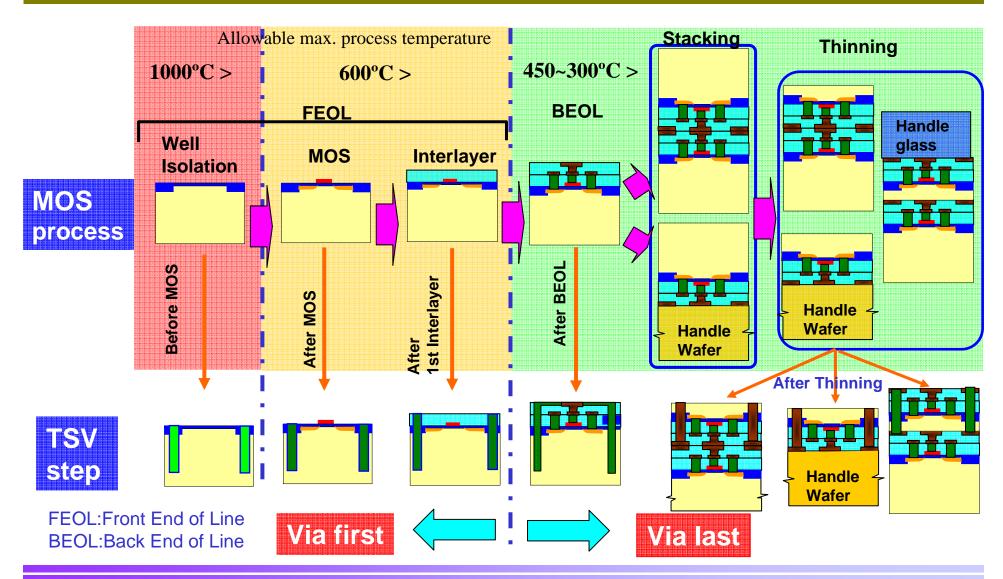

#### **TSV process Choice Via First or Via Last**

TSVs with very wide range of diameter can be realized now. But there are few solution which satisfy target application, base wafer supply chain, purpose of productize 3D-LSI.

Copyright © ZyCube Co., Ltd. All rights reserved

# TSV process classification

# **Outline**

- 1. Introduction

- Advantages of 3D-LSI

- Potential Application

## 2. Technology Approach

- Technology breakdown

- TSV scaling, process

- Bond/Stack approaches

## 3. TSV and $\mu$ -bump

- Current technology

- **3D-LSI for Image Sensor**

- Next generation technology

#### 4. Summary

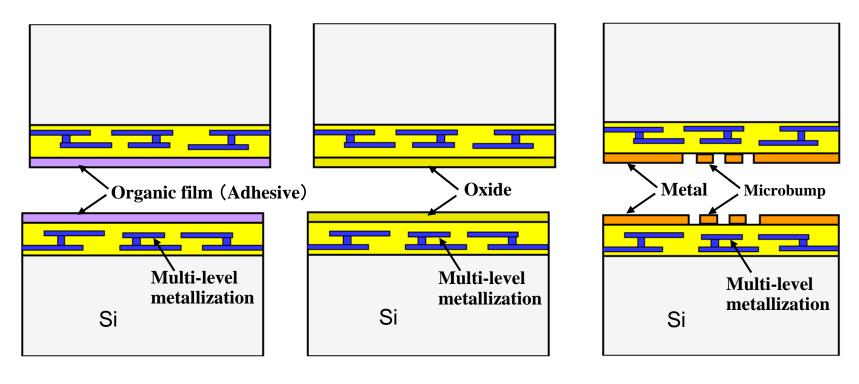

#### Various Kinds of Wafer Bonding Methods (1)

**Adhesive Bonding**

Direct Oxide Bonding

**Direct Metal Bonding**

#### Various Kinds of Wafer Bonding Methods (2)

Adhesive/ Metal Bonding

Oxide/ Metal Bonding

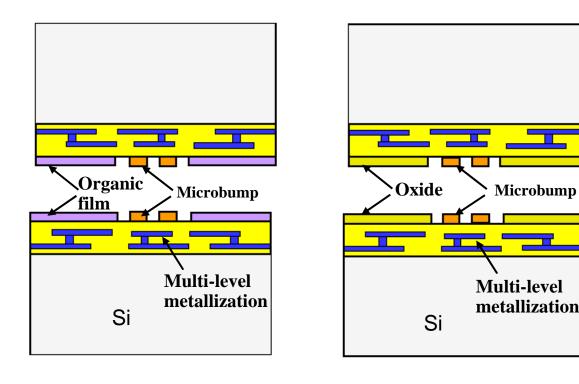

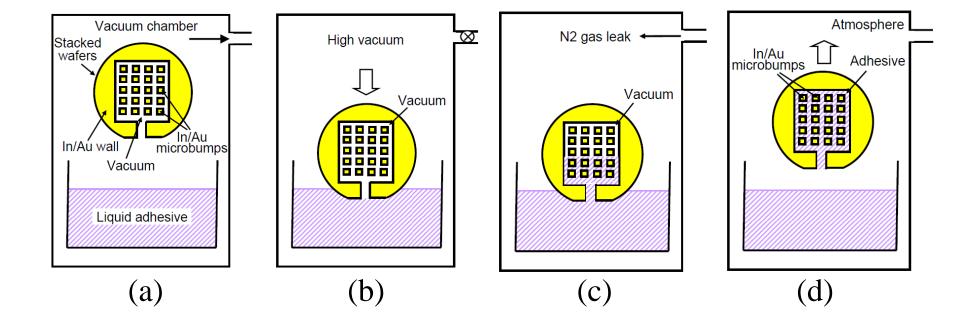

#### Various Kinds of Wafer Bonding Methods (3)

(Tohoku University)

Wafer Alignment

Temporary Bonding (Metal Bonding)

Adhesive Injection

#### **Process Sequence of Adhesive Injection Method**

T. Matsumoto and M. Koyanagi et al, SSDM, pp.460-461, 1997.

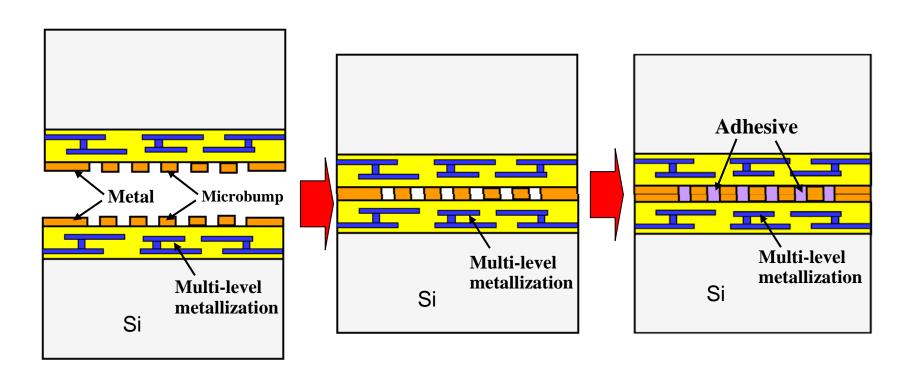

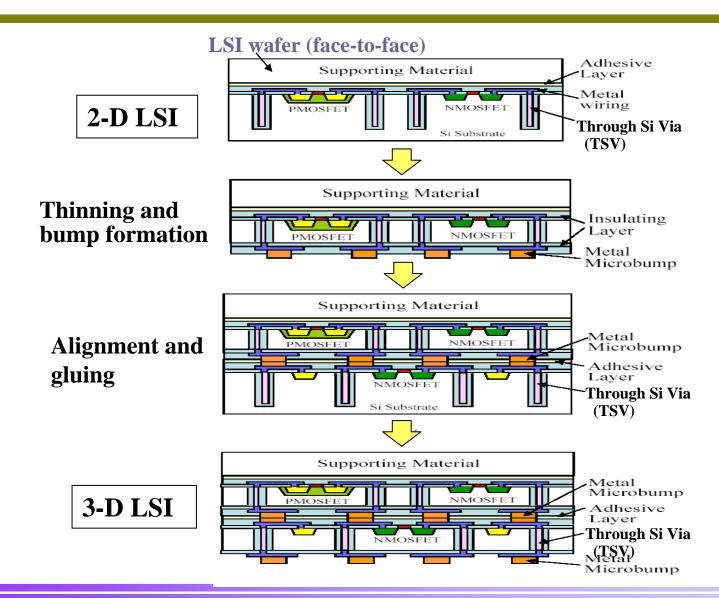

#### **Fabrication Sequence of 3D LSI**

# **Outline**

#### 1. Introduction

- Advantages of 3D-LSI

- Potential Application

## 2. Technology Approach

- Technology breakdown

- TSV scaling, process

- Bond/Stack approaches

## 3. TSV and $\mu$ -bump

Current technology

**3D-LSI for Image Sensor**

Next generation technology

#### 4. Summary

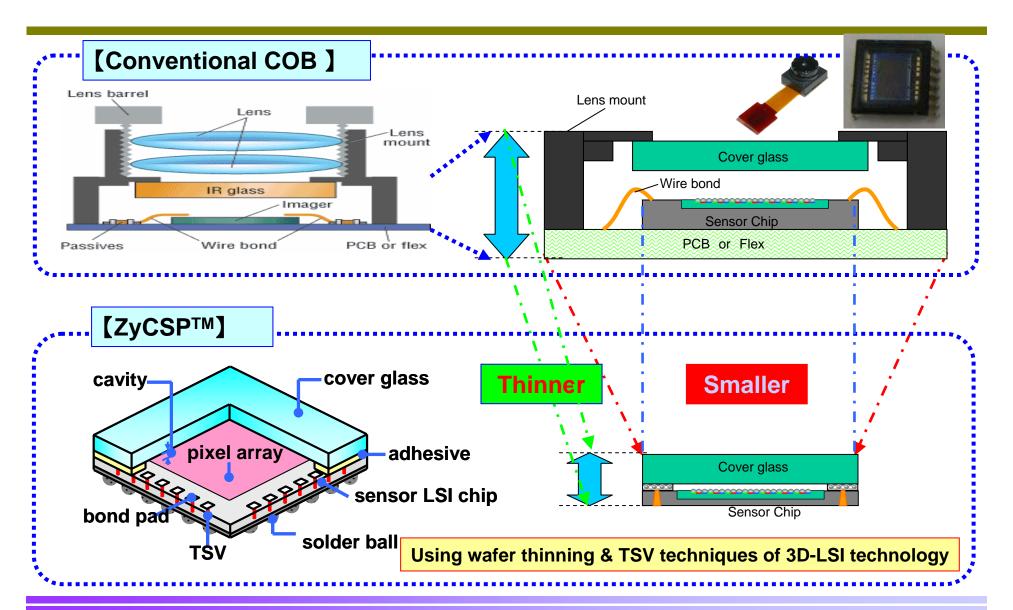

#### The necessity of 3D-LSI Technologies for an Image sensor

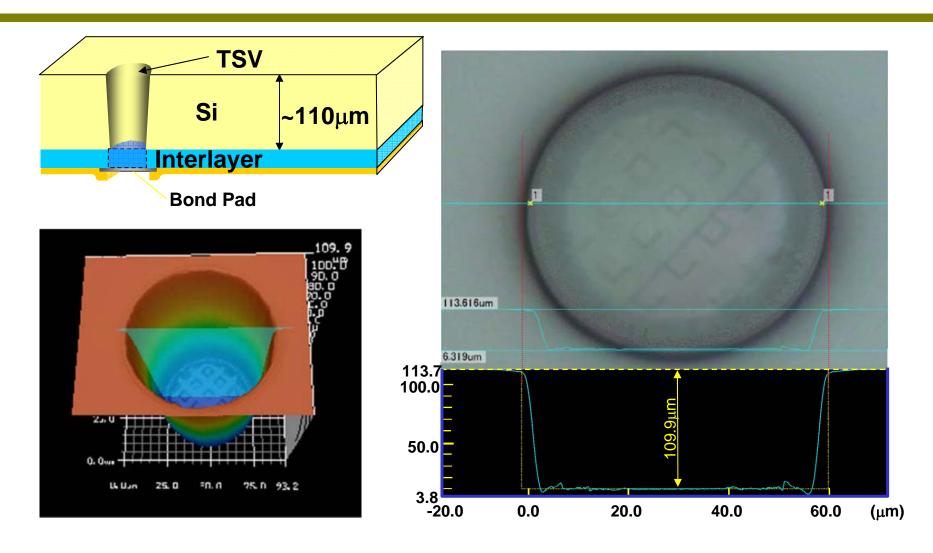

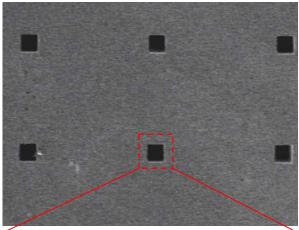

# 50μmφ (80μm pitch) TSV

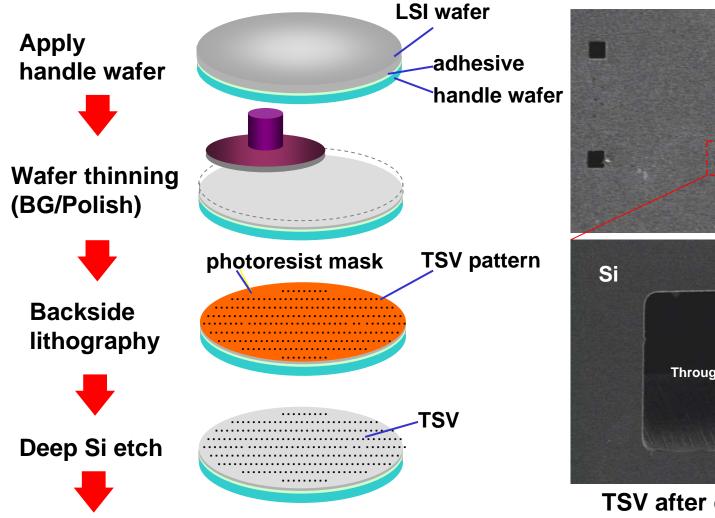

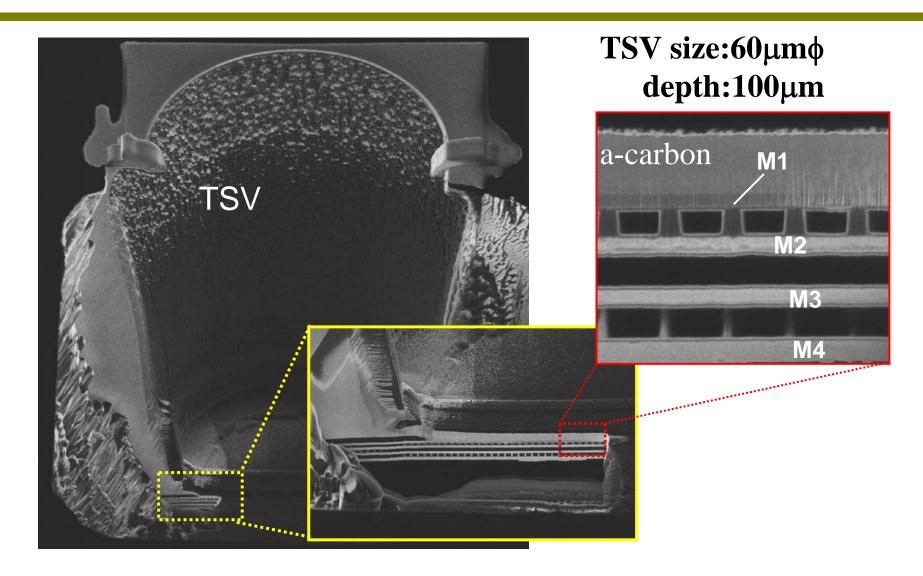

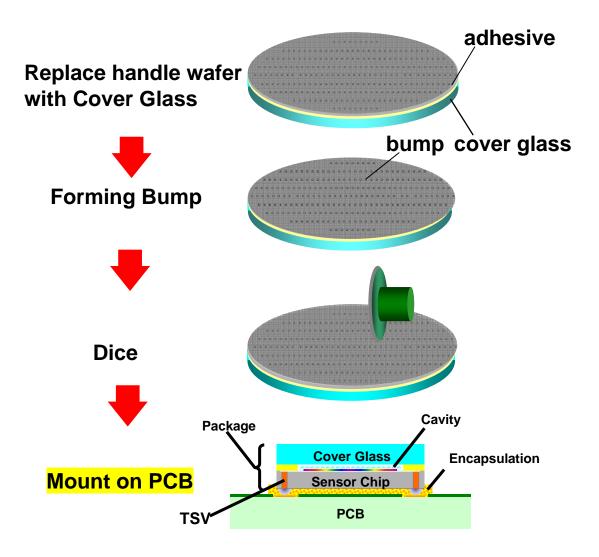

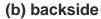

# **ZyCSP<sup>TM</sup> Process Sequence (1)**

TSV after deep Si etch

# TSV after SiO<sub>2</sub> RIE

28

# **ZyCSP<sup>TM</sup> Process Sequence (2)**

# **ZyCSP<sup>TM</sup> Process Sequence (3)**

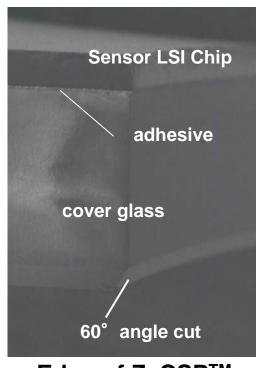

Edge of ZyCSP™

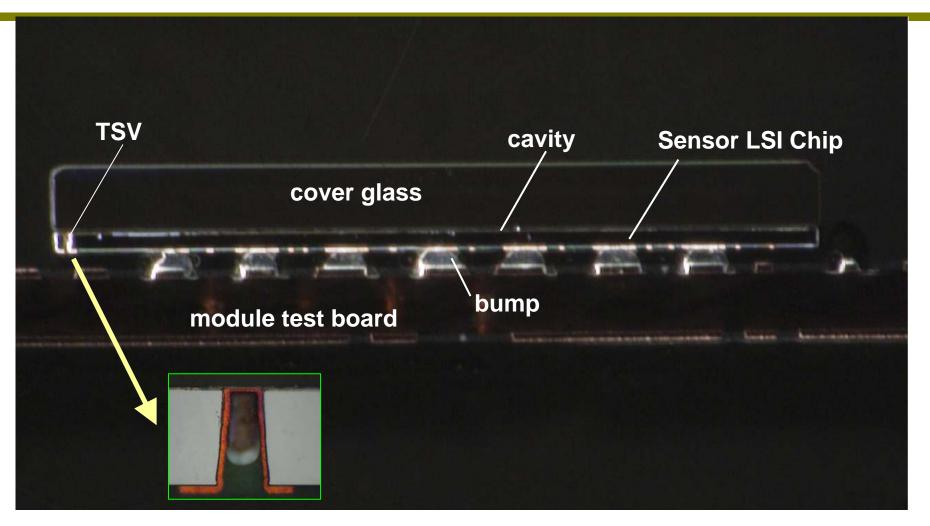

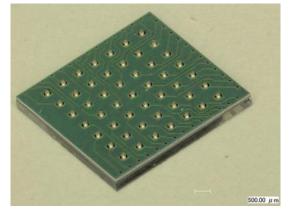

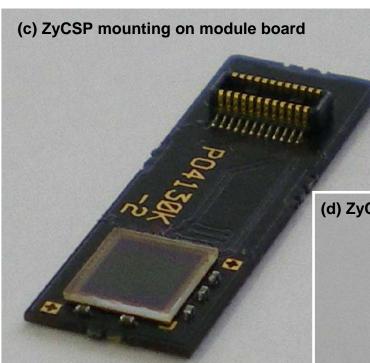

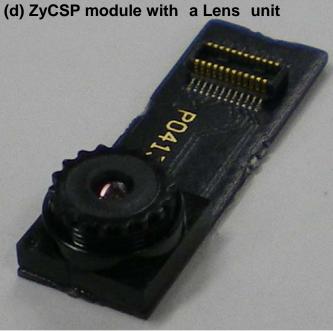

# **ZyCSP<sup>TM</sup>** mounting on the test board

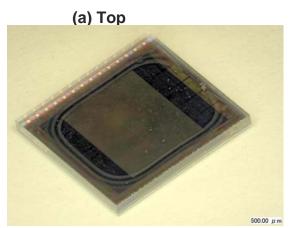

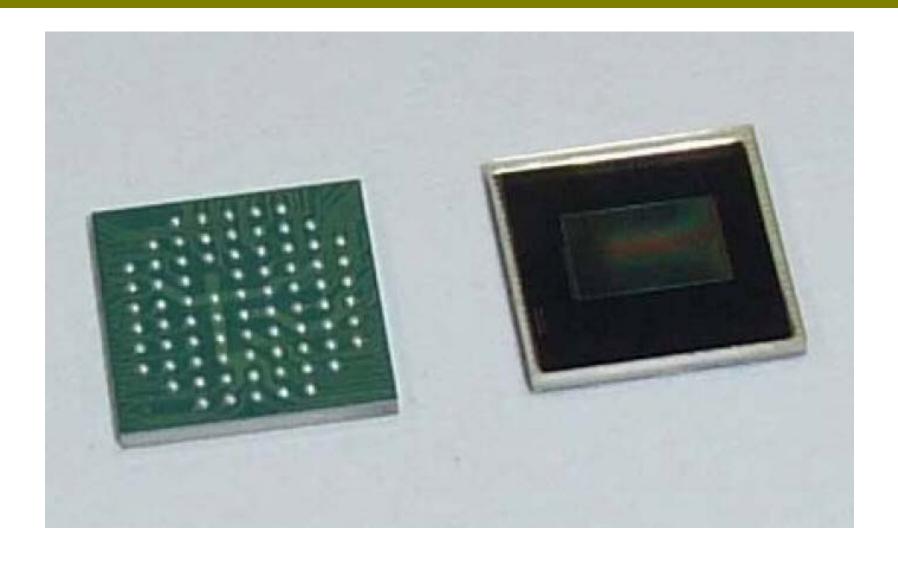

# **Exercise** The ZyCSP<sup>TM</sup> for the camera module

#### 1.3M pixel Sensor LSI

# 2M pixel Sensor CSP

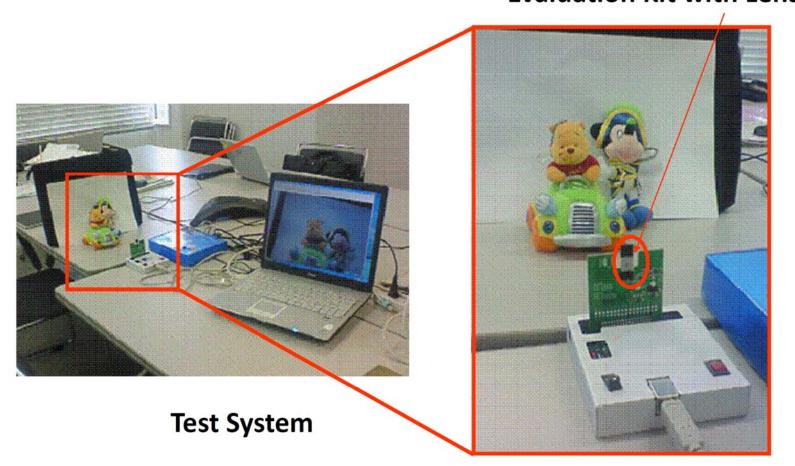

# **Working Sample Test System**

#### **Evaluation Kit with Lens**

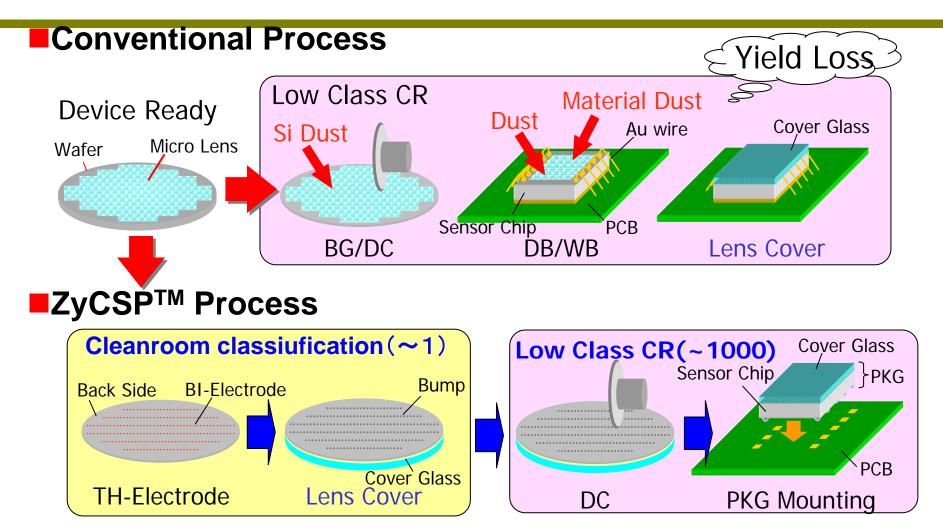

## **Fabrication Processes Comparison**

High Yield utilizing Wafer Level Process

# **Outline**

- 1. Introduction

- Advantages of 3D-LSI

- Potential Application

- 2. Technology Approach

- Technology breakdown

- TSV scaling, process

- Bond/Stack approaches

- 3. TSV and  $\mu$ -bump

- Current technology

3D-LSI for Image Sensor

- Next generation technology

- 4. Summary

#### **Current 3D-LSI Technologies**

#### **Advantages**

- -Available to use existing LSI chip design w/o or w/ minor modification

- -Reduce foot print eg. multifunctional SoC, High density memory

Get the best performance out of 3D-LSI

**Next Generation 3D-LSI Technologies**

#### **Next Generation 3D-LSI Technologies**

5Key technologies

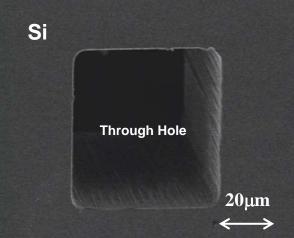

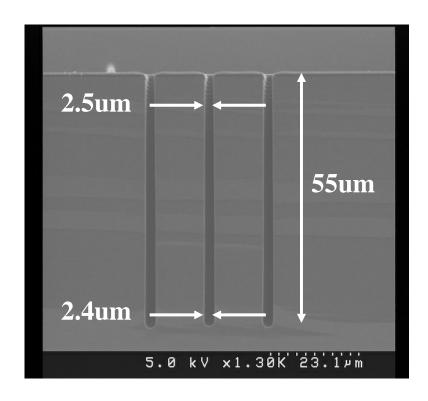

#### **SEM Cross Section of Poly-Si TSV**

(Via first)

(a) Si deep trench etching

(b) Filling with Poly-Si

T. Matsumoto and M. Koyanagi et al., SSDM, 1995.

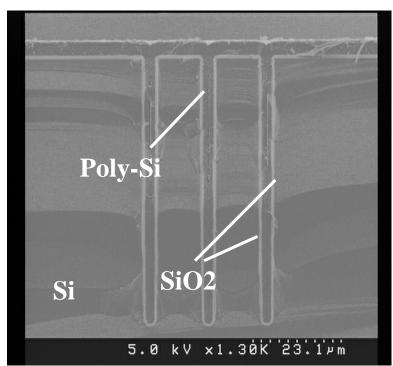

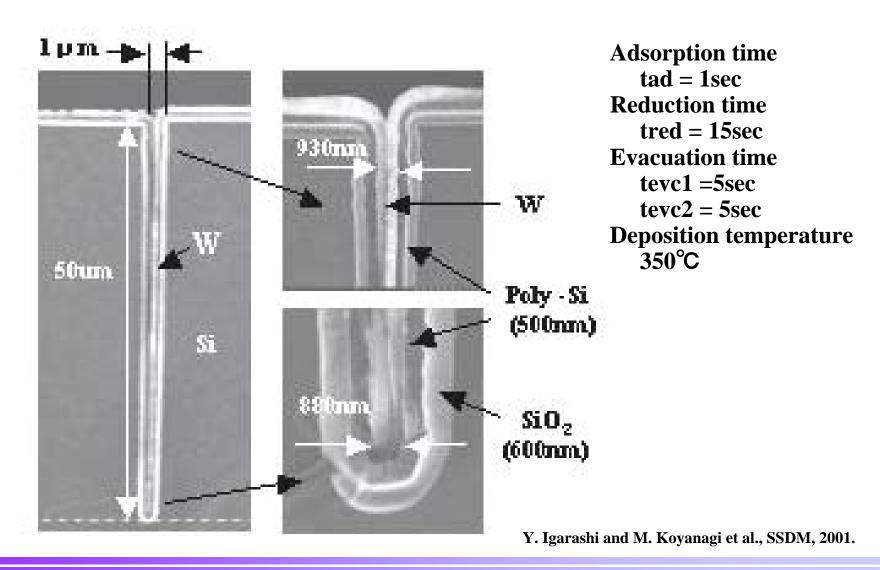

#### SEM Cross Section of W/ Poly-Si TSV

(Via first or Via before BEOL)

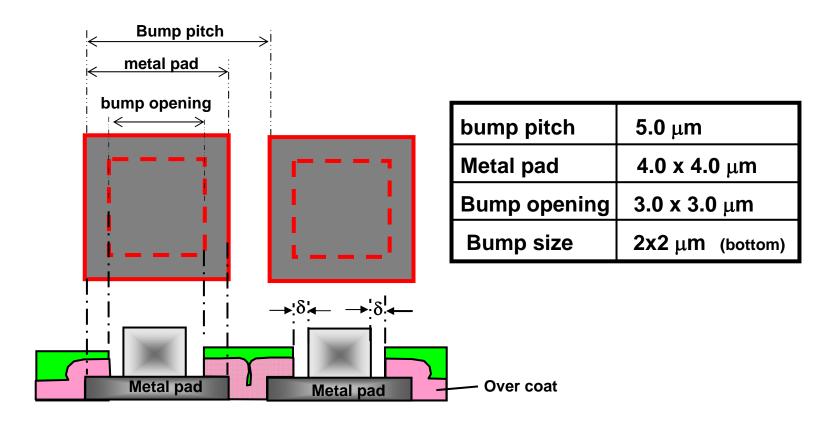

# Schematic Diagram of micro-bump structure using new micro-bump fabrication process

Clearance groove ( $\delta$ ) between bump opening and bump are formed by self-aligned process

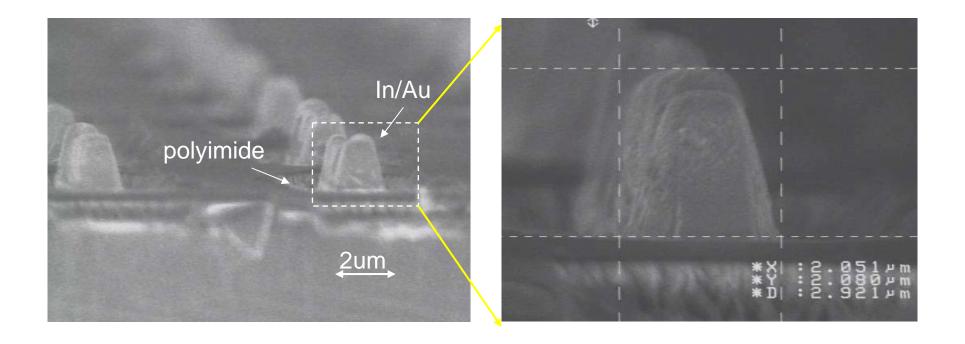

# 2μm x 2μm Bumps

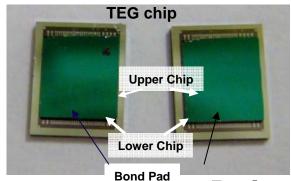

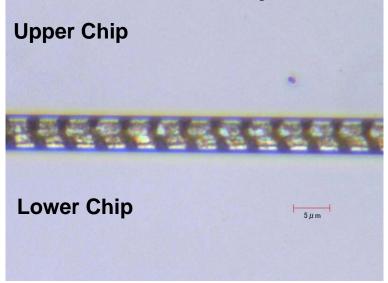

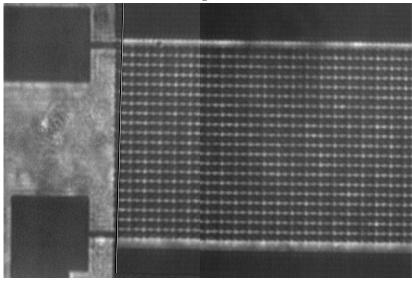

## 5μm pitch μ-bump

Daisy Chain with 10<sup>4</sup> m-bumps

**Cross section**

Plain View (IR microscope)

Tohoku Univ. / ZyCube

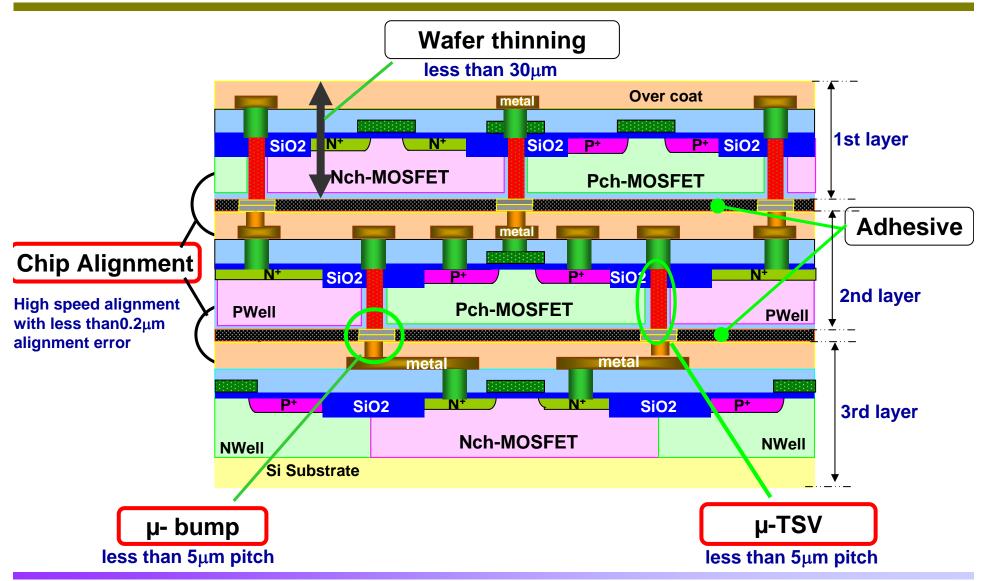

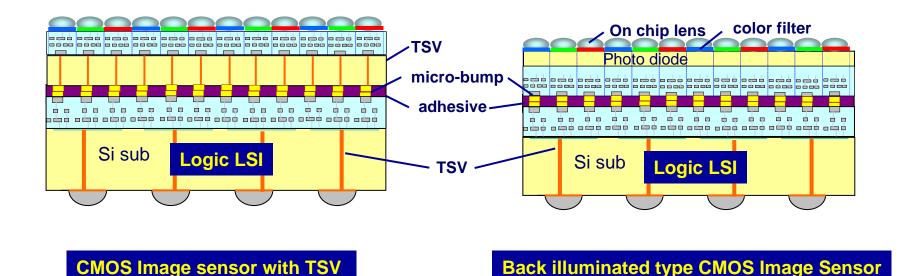

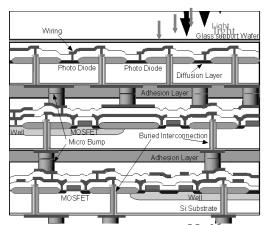

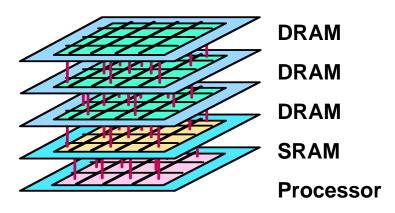

## Image sensor module with μ-bump & μ-TSV

By connecting the back illuminated type CMOS image sensor to Logic LSI, a high speed Pixel detector system with 100% fill factor will be realize.

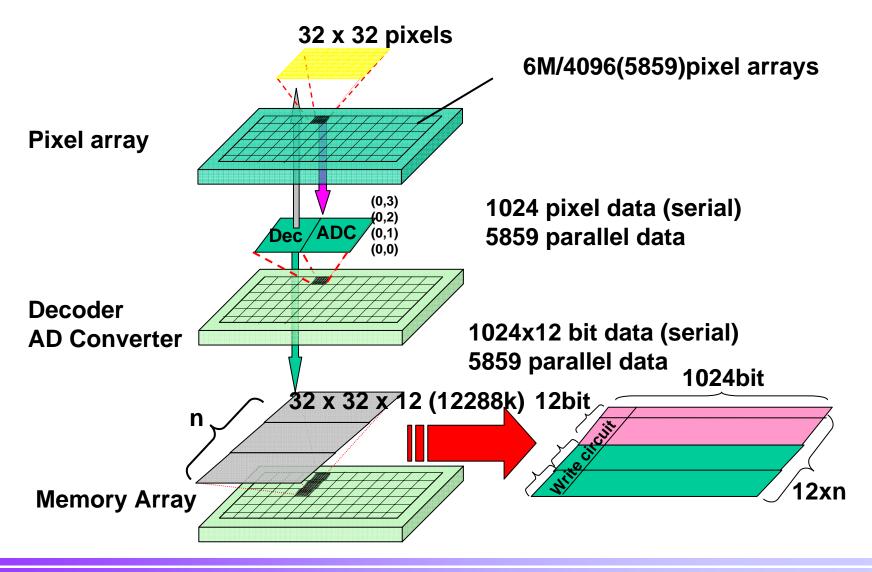

## High Speed Parallel Processing Image Sensor with Memory

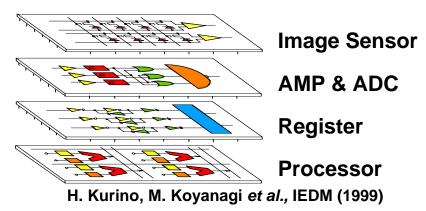

### 3D LSI Prototype Chips Fabricated in Tohoku Univ.

### **Real-Time Image Processing System**

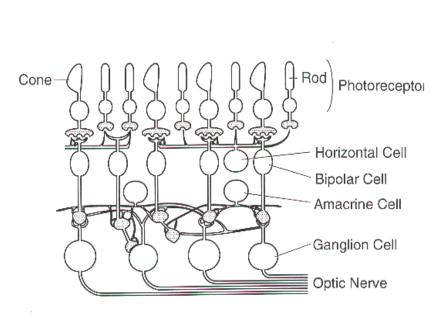

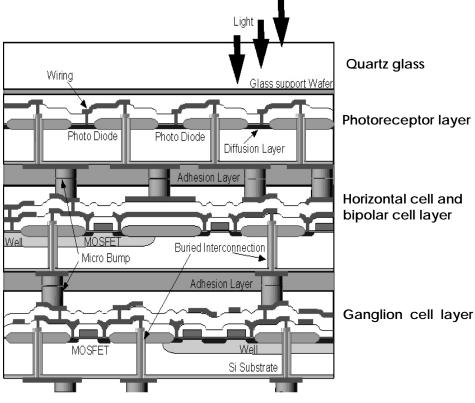

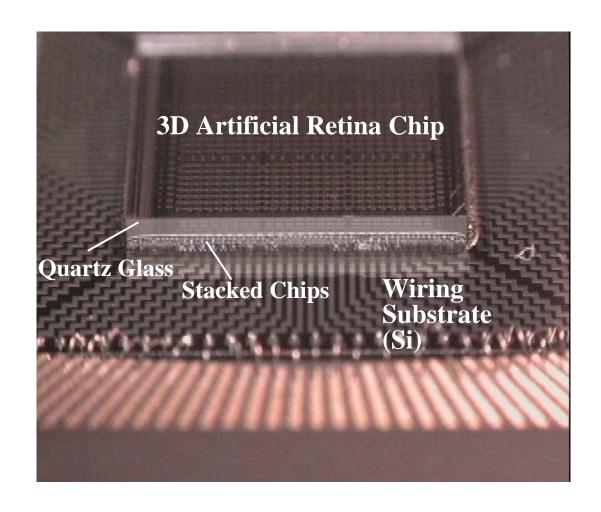

### 3D artificial retina chip

**Quartz glass** Photoreceptor layer

Horizontal cell & bipolar cell layer

Ganglion cell layer

M. Koyanagi et al., ISSCC (2001)

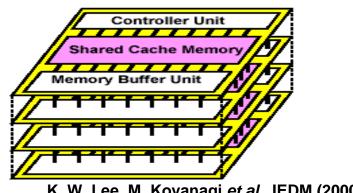

### **3D shared memory**

K. W. Lee, M. Koyanagi et al., IEDM (2000)

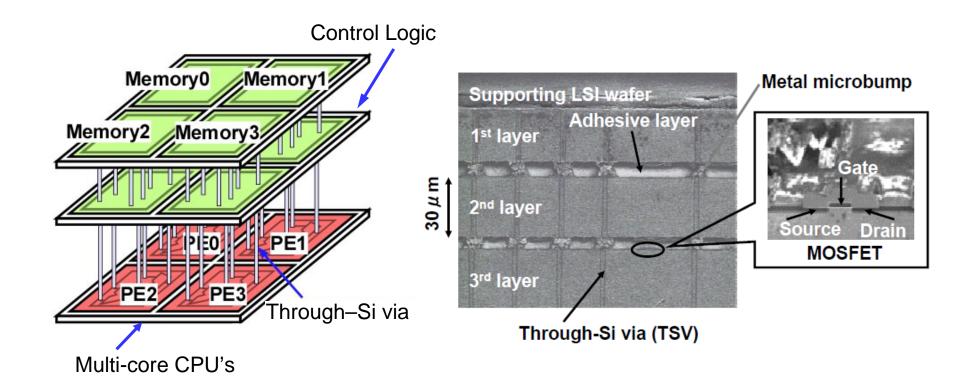

### 3D microprocessor chip

T. Ono, M. Koyanagi et al., IEEE COOL Chips (2002)

### **ZyCube**

### SEM Cross-Sectional View of 3-D Microprocessor Chip Fabricated by Wafer-to-Wafer Bonding

# **Cross-Sectional Structures of Human Retina and 3D Artificial Retina Chip**

(a) human retina

(b) 3D retina chip

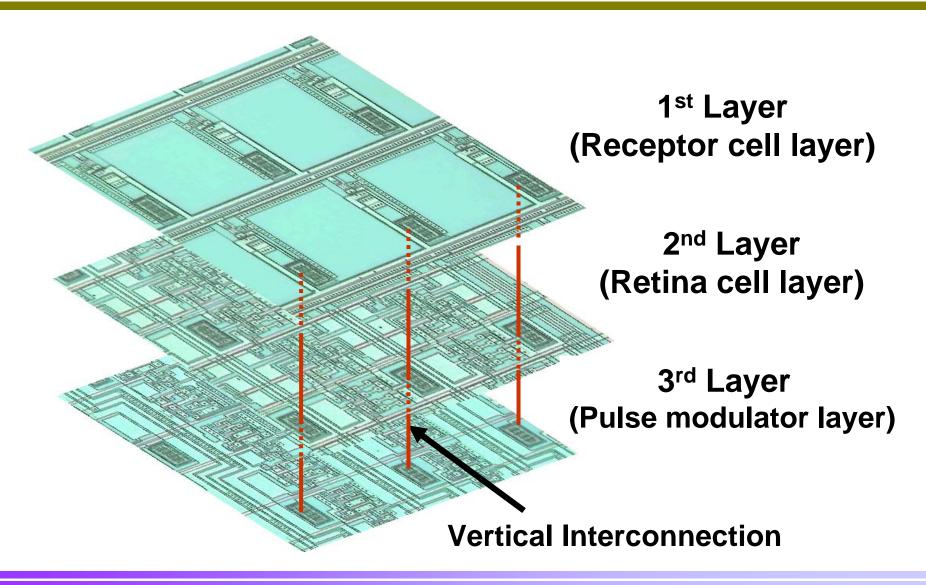

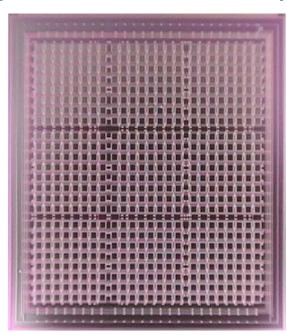

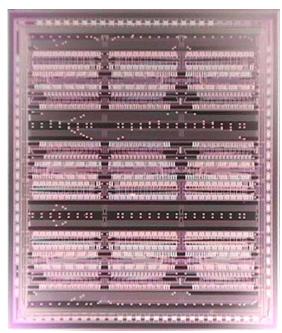

### Photograph of 3D Artificial Retina Chip

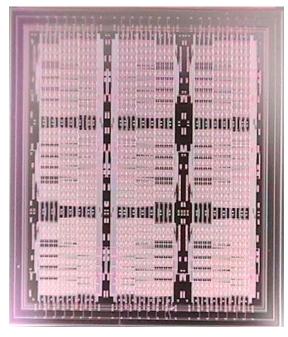

# Photograph of Respective Chip in 3D Stacked Image Sensor Chip with Three Stacked Layers

1<sup>st</sup> Layer (Photosensor circuit)

2<sup>nd</sup> Layer (Register circuit)

3<sup>rd</sup> Layer (ADC & ALU circuit)

(Chip size : 6 mm x 6 mm, 112 pins )

### Photomicrograph of 3D Artificial Retina Chip

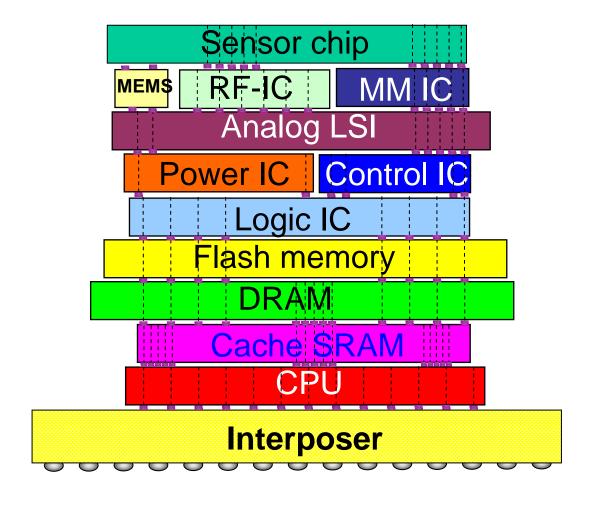

### **Configuration of 3D Super Chip**

### **Current 3D-LSI stack approaches**

|                                           | COC (chip on chip) | COW (chip on wafer) | WOW (wafer on wafer)   |  |

|-------------------------------------------|--------------------|---------------------|------------------------|--|

|                                           | stack              | dicing              | dicing                 |  |

| Process cost                              | High               | High~Middle         | Low                    |  |

| Stack chips with different chip size      | Easy               | Easy                | Impossible             |  |

| Chip alignment<br>accuracy<br><0.2μm (3σ) | Difficult from ec  | possible ?          |                        |  |

| Miscellaneous                             |                    |                     | Need high yield wafers |  |

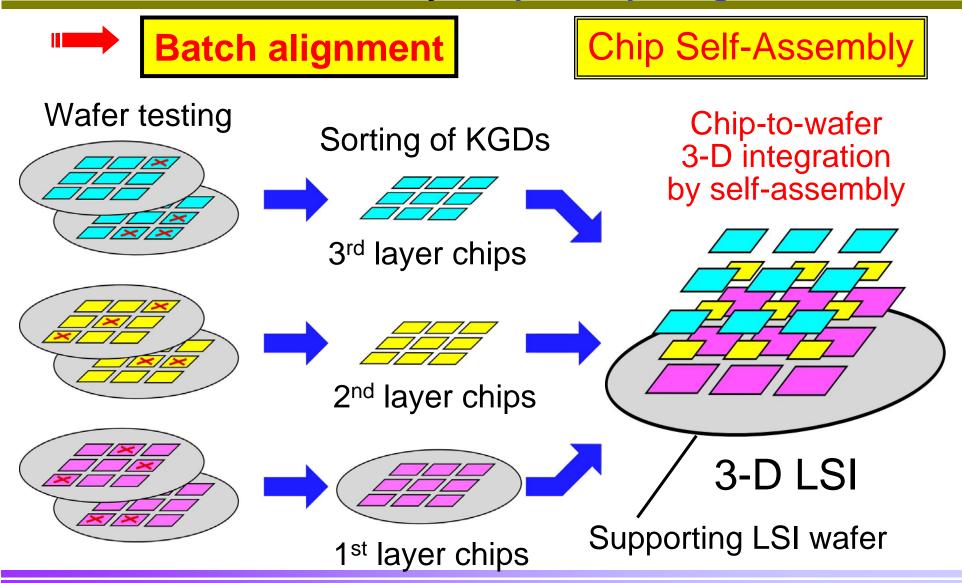

Need a high speed COW technology with the high alignment accuracy and the practical process cost

### High speed and high accuracy Chip Alignment

### Requirement

Alignment Error < 0.2um

TAT (turn around time) ~ wafer process

In order to reduce cost, short process time (batch process) is indispensable

# 3-D Technology Based on New Chip-to-Wafer Bonding in Tohoku University: Super-Chip Integration

### 3D-LSI Process Selection -- Which is best ?--

| TSV process<br>Conductor Mat. |              | Via first                                |                                            | Via last                                                                                  |                                                                    | G               | ck<br>erent                              |

|-------------------------------|--------------|------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------|------------------------------------------|

| Stack<br>Approach             |              | Before MOS                               | FEOL<br>(After MOS)                        | after BEOL<br>before Stack                                                                | after Stack                                                        | Process<br>cost | Chip Stack<br>with differen<br>chip size |

|                               |              | Poly-Si                                  | Poly-Si, W                                 | W, Cu, etc                                                                                | W, Cu, etc                                                         | ₫               | Chip<br>with o                           |

| VVOVV                         | Bulk         | Tohoku Univ.<br>(ZyCube)<br>IBM<br>Dalsa | TSMC Tezzaron RPI Ziptronix Chartered Semi | Tohoku.U<br>ZyCube<br>Toshiba<br>Samsung<br>IMEC                                          | Ziptronix<br>Albany NanoTech<br>IMEC<br>Samsung                    | Low             | Impossib                                 |

|                               | soı          |                                          |                                            | Tohoku.U                                                                                  | IBM<br>MIT(Lincoln Lab.)<br>RPI                                    |                 |                                          |

| CoW w<br>self-as<br>technic   | sembly       | Tohoku U.                                |                                            | Frounhofer IZM ZyCube/Tohoku U. Samsung CEA-LETI Ziptronix IMEC                           |                                                                    | Low             | Easy                                     |

| CoC                           | ;            | Tohoku U.<br>Elpida                      |                                            | ZyCube<br>ASET<br>Intel, Infineon, IMEC,<br>Samsung, Toshiba,<br>Fujitsu<br>Renesas ,NEDO | <sidewall connection=""><br/>TESSERA<br/>3Dplus<br/>VCI</sidewall> | High            | Easy                                     |

| Stack i<br>wafer p            | n<br>process | NAND M                                   |                                            | Γ-NAND(Samsung)<br>S-NAND(Toshiba)                                                        |                                                                    |                 |                                          |

## **Summary**

- 1. The Current & future 3D-LSI technologies with TSV were described.

- 2. Advantages of 3D-LSIs are

- (a) Increase of electrical performances

- (b) Increase of circuit density

- (c) New Architecture (Hyper-parallel processing, Multifunction, etc)

- (d) Heterogeneous integration

- (e) Cost reduction

- 3. Many 3D-Integration approach have been reported. Considering supply chain of the base LSIs and variety of application, it is difficult to unify.

- 4. The CSP for 1.3M pixel CMOS image sensor was successfully fabricated without performances degradation.

- 5. By connecting the back illuminated type CMOS image sensor to Logic LSI, a high speed Pixel detector system with 100% fill factor will be realize.

- 3. In order to enter mass market for 3D-LSI, suppressing a rise in price of chip stack is essential. In this standpoint, for realizing 3D-Super chip, the high speed and high accurate CoW will be indispensable.