## SOI技術を用いた計数型Pixel検出器の性能評価

# 大阪大学大学院 理学研究科物理学専攻 山中卓研究室 博士前期課程2年

内田 潤

March 2, 2011

#### 概要

本研究の目的は、Silicon-On-Insulator (SOI) 技術を用いて開発された一体型の Pixel 検出器 (以下 SOIPIX 検出器) のうち、計数型と呼ばれる検出器 (以下計数型 SOIPIX 検出器) の性能を評価することである。評価した内容はアナログ特性と X 線などに対する反応の二つである。前者についてはセンサー部分のダイオード特性の測定や回路部分の X gain の測定を行った。後者に関しては可視光、 X 線そして X 線に対する反応を確認した。これら一連の試験により計数型 SOIPIX 検出器の動作の評価を行い、正常に動作することを確認した。

## 目 次

| 第1章 | 序章                                           | 5  |

|-----|----------------------------------------------|----|

| 1.1 | 半導体検出器とその利用                                  | 5  |

| 1.2 | SOI 検出器について                                  | 5  |

|     | 1.2.1 SOI 技術                                 | 5  |

|     | 1.2.2 SOI 検出器の概要                             | 6  |

|     | 1.2.3 SOI 検出器の開発状況                           | 7  |

| 1.3 | 本研究の目的                                       | 8  |

| 第2章 | 半導体検出器                                       | 9  |

| 2.1 | 半導体とキャリア・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 9  |

| 2.2 | 不純物半導体                                       | 9  |

| 2.3 | p-n 接合と半導体検出器                                | 11 |

| 第3章 | 計数型 SOI ピクセル検出器                              | 12 |

| 3.1 | 計数型 SOI ピクセル検出器の構造                           | 12 |

|     | 3.1.1 CNTPIX4 <b>の全体構造</b>                   | 12 |

|     | 3.1.2 CNTPIX4 <b>のピクセル構造と動作</b>              | 13 |

|     | 3.1.3 Control Register                       | 13 |

| 3.2 | カウンター値の読み出し                                  | 14 |

| 第4章 | 計数型 SOIPIX 検出器のアナログ特性                        | 16 |

| 4.1 | 測定対象と用いた検出器                                  | 16 |

| 4.2 | センサー部分のダイオードの I-V 特性                         | 16 |

| 4.3 | アナログ回路のパラメータの調整                              | 17 |

|     | 4.3.1 2 つの VREF の調整                          | 17 |

| 4.4 | Gain <b>測定</b>                               | 19 |

| 第5章 | 動作試験                                         | 21 |

| 5.1 | DAQ システムの開発                                  | 21 |

|     | 5.1.1 読み出し用汎用ボード:SEABAS                      | 21 |

|     | 5.1.2 SubBoard                               |    |

|     | 5.1.3 DAQ <b>の流れ</b>                         |    |

|     | 5.1.4 DAQ 用プログラム                               | 23 |

|-----|------------------------------------------------|----|

| 5.2 | カウンターの動作テスト                                    | 24 |

| 5.3 | 可視光に対する応答・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・  | 24 |

| 5.4 | X 線に対する応答                                      | 25 |

|     | 5.4.1 X 線に対する応答の確認                             | 25 |

|     | 5.4.2 X <b>線の強度とカウンター</b> 出力 :                 | 26 |

| 5.5 | X 線照射前後での性能の変化                                 | 27 |

|     | 5.5.1 X 線照射と preamp の gain                     | 27 |

|     | 5.5.2 X 線照射に伴う残像                               | 28 |

| 5.6 | 放射線源に対する応答・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 28 |

| 5.7 | Back gate effect                               | 29 |

|     | 5.7.1 Back gate effect $\succeq$ BPW           | 29 |

|     | 5.7.2 計数型 SOI 検出器における BPW の効果                  | 30 |

| 第6章 | まとめと考察                                         | 32 |

| 6.1 | アナログ回路                                         | 32 |

| 6.2 | 動作試験                                           | 32 |

| 6.3 | BPW について                                       | 33 |

| 6.4 | X 線照射に伴うカウンターの異状について                           | 33 |

| 第7章 | ·····································          | 35 |

## 図目次

| 1.1                                           | SOI CMOS トランジスタ                                                             | 7                    |

|-----------------------------------------------|-----------------------------------------------------------------------------|----------------------|

| 2.1<br>2.2<br>2.3                             | シリコンのエネルギー準位のバンド構造の模式図アクセプター準位。ドナー準位。                                       | 10<br>10<br>10       |

| 3.1<br>3.2<br>3.3<br>3.4                      | CNTPIX4。                                                                    | 12<br>13<br>14<br>15 |

| 4.1<br>4.2<br>4.3                             | センサー部分のダイオードの I-V 特性                                                        | 17<br>18             |

| 4.4<br>4.5                                    | preamp の出力は水色である。                                                           | 19<br>19             |

| 4.6<br>4.7                                    | じ。                                                                          | 19<br>20<br>20       |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | SEABAS                                                                      |                      |

| 5.4<br>5.5<br>5.6                             | DAQ システム                                                                    |                      |

|                                               | 実験に用いたマスク。<br>CPIXTEG1 にマスク越しに LED を照射した画像。<br>CPIXTEG1 にマスク越しに X 線を照射した画像。 | 25                   |

|                                               | カウンター出力の管電流依存性。縦軸はカウンター出力を管電流の<br>値の比である。                                   | 26<br>27             |

| 5.12 | X 線照射後の preamp の gain。           | 28 |

|------|----------------------------------|----|

| 5.13 | カウンター出力の紫外線照射による回復。              | 29 |

| 5.14 | 放射線源が無い場合。                       | 30 |

| 5.15 | 放射線源を用いた場合。                      | 30 |

| 5.16 | BPW 未実装のピクセルの出力の X 線強度依存性。       | 31 |

| 5.17 | カウンター出力の $V_{back}$ 依存性。 $\dots$ | 31 |

## 第1章 序章

この章では本研究の目的とSOI検出器について簡単に述べる。

## 1.1 半導体検出器とその利用

半導体検出器はその位置分解能の高さなどから、現在の高エネルギー物理学にとって不可欠な検出器となっている。半導体検出器は数十 $\mu$ m という高い位置分解能を持っており、荷電粒子の飛跡や崩壊点などを精度良く決定するために利用されている。

また高エネルギー物理学分野以外でも半導体検出器の利用範囲は広く、これにはデジタルカメラなど我々が日常的に使用しているものも含まれる。このように半導体検出器は幅広い分野で利用されており、今後もその利用範囲は拡大していくものと予想される。

## 1.2 **SOI**検出器について

#### 1.2.1 SOI 技術

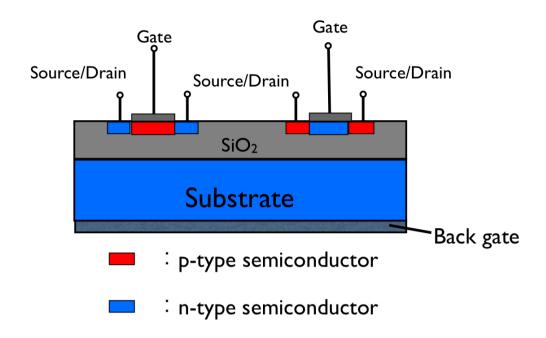

SOI とは Silicon-On-Insulator の略であり、シリコンウェハーの上に薄い絶縁酸化膜を作り、さらにその上に形成したシリコンウェハー上に電気回路 (トランジスタなど)を形成する技術のことである。絶縁膜が存在するため Bulk CMOS トランジスタに比べてリーク電流や寄生容量を少なくすることができ、消費電力の抑制などが可能になる。現在では、例えば一般的な PC に用いられている CPU の製造は SOI 技術を用いたものが主流となっている。

#### 1.2.2 SOI 検出器の概要

図 1.1 のように、支持基盤をセンサーとして、また絶縁層上に形成した電気回路をセンサーからの信号の読み出しに使用するように設計された半導体検出器をSOIPIX 検出器と呼ぶ。SOIPIX 検出器の最大の特徴はセンサー部分と読み出し用の回路部分を同じ基板上に作成する点である。現行のピクセル検出器ではセンサーと読み出し回路は別のウェハーを用いて作成され、それらをバンプボンディングにより接続しているのに対して、SOIPIX 検出器の場合にはボンディングは不要である。ボンディングされたものに比べて扱いやすく、また歩留まりが良くなるため価格を抑えることが可能である。

その他 SOIPIX 検出器の利点としては次のようなものが挙げられる。

#### ・薄型化

1つの基板で検出器として成り立っていことから、検出器を薄くすることができる。これは検出器を通過する荷電粒子の多重散乱の抑制に効果がある。

#### ・読み出しの高速化

絶縁層があることで回路部分の接合容量が減少する。これにより読み出し回路の時定数が小さくなるため、読み出し回路の動作を高速化できる。結果として読み出し速度の高速化が可能になる。

#### ・低消費電力

SOIPIX 検出器ではセンサー部分と回路部分が絶縁層によって絶縁されているため、リーク電流が減少する。これにより消費電力の抑制、すなわち発熱を減らせ、高エネルギー物理学実験のように大量の検出器を必要とする実験での電源系や冷却系の負担を軽減することができる。また宇宙空間など電力供給が限られている環境で使用する場合にも、消費電力の低さは有利に働く。

#### ・高集積性

SOI CMOS では絶縁膜の存在により隣接する素子同士の影響を抑えることができるため、素子間の距離を短くすることができる。これは高集積化につながる。

図 1.1: SOI CMOS トランジスタ

#### 1.2.3 SOI 検出器の開発状況

SOI 検出器開発プロジェクトは、KEK の SOIPIX グループの主導で進められている。これまで年に二回から三回のペースでプロトタイプの製造を行っている。 SOIPIX グループが開発している SOIPIX 検出器には大きく分けて積分型と呼ばれるものと計数型と呼ばれるものがある。

積分型 SOIPIX 検出器は粒子線検出を目的として開発が進められている。検出器に粒子線が入射すると、粒子線がセンサー部分で失ったエネルギーに応じた電荷が生成さる。生成された電荷量を測定するために、積分型 SOIPIX 検出器では電荷を一定時間、回路部分に蓄積する (このため積分型と呼ばれている)。各ピクセルの回路に蓄積された電荷をデジタル値に変換することで、エネルギー情報を取得する。

一方、計数型 SOIPIX 検出器は二つの閾値を持っていて、一定時間内にセンサーに入射した粒子のうち、二つの閾値の間のエネルギーを持ったものの数を保存するように設計された検出器である (この機能のため計数型と呼ばれている)。粒子がセンサーに入射した時に生成される電荷が回路に入力されると、入力された信号ごとにエネルギーの弁別が行われ、一定以上のエネルギーを持った信号の数を記録する。この性質を利用した主な応用例としては X 線の強度測定がある。

SOIPIX 検出器開発は現在は基礎開発の段階にあり、Back gate effect (5.9 節で触れる)と呼ばれる SOI 検出器特有の問題などの解決に取り組んでいる。現在のところまだ実用化には至っていないが、現段階でも積分型、計数型ともに可視光に反応していることが確認されるなど一定の成果が出ている。

## 1.3 本研究の目的

本研究の目的は計数型 SOIPIX 検出器の性能評価である。計数型 SOIPIX 検出器 に関しては過去の研究で可視光や X 線に対する応答などが確認されているが、アナログ特性などの系統的な検証はされていない。今回の研究では主に計数型 SOIPIX 検出器の動作確認用に設計された CPIXTEG1 と呼ばれるプロトタイプ検出器を利用して、センサー部分のダイオード特性や X 線に対する反応を評価した。

## 第2章 半導体検出器

この章では半導体検出器について簡単に説明する。

### 2.1 半導体とキャリア

高エネルギー物理学で主に利用されている半導体にはシリコンやゲルマニウムがある。ここでは、本研究で用いた SOIPIX がシリコンを用いた半導体検出器であることをふまえて、シリコンについて説明する。

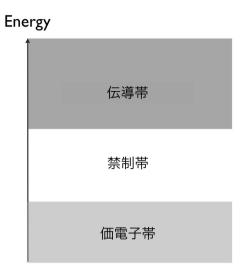

シリコンのエネルギー準位のバンド構造は図 2.1 のようになっている。バンド構造はエネルギーの低い方から順に、価電子帯、禁制帯、伝導帯と呼ばれている。このうち電荷の運び手であるキャリアとなるのは伝導帯に存在する電子であるが、禁制帯は電子が存在できないエネルギー領域であるため、価電子帯に存在する電子は伝導帯と価電子帯のエネルギー差以上のエネルギーを受け取り、伝導帯へ励起されて初めてキャリアとなる。また伝導帯に電子が移った後の価電子帯には、電子が存在しない穴ができる。これは相対的に正の電荷を運ぶキャリアとして働くため正孔と呼ばれる。

純粋なシリコン結晶であっても、熱励起により伝導帯へ励起した電子が存在することで多少の導電性を示すため、半導体と呼ばれている。

### 2.2 不純物半導体

純粋なシリコンの結晶に3価や5価の元素を不純物として添加したものを不純物半導体という。不純物を添加したシリコンは純粋なシリコンに比べて伝導性が変化する。

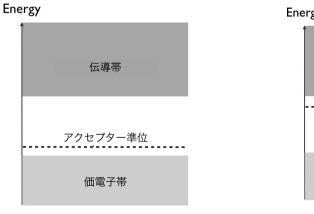

まず3価の元素を添加した場合を考える。シリコンは4価の元素であるため、3価の元素を添加した場合には結晶内の共有結合に使われる電子が1つ不足することになり、この電子の足りない穴が正孔として振る舞う。こうしてできた正孔の作る準位が図2.2に示すように価電子帯のすぐ上に形成されるため、純粋なシリコン結晶に比べて伝導帯に電子が遷移しやすくなる。価電子帯の電子がこの新たにで

図 2.1: シリコンのエネルギー準位のバンド構造の模式図

きた準位に遷移すると価電子帯に正孔ができることとなり、結晶は伝導性を持つ。 このような半導体はp型半導体と呼ばれ、添加された3価の元素とをアクセプター と呼ばれる。また新たに形成されたエネルギー準位をアクセプター準位と呼ぶ。

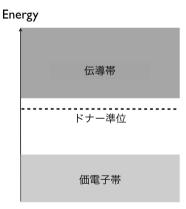

一方、シリコン結晶に 5 価の元素を添加すると、今度は共有結合に使われる電子が1つ余り、今度はこの電子が図 2.3 に示すように伝導帯のすぐ下にエネルギー準位を形成する。この電子は価電子帯にある電子と比べて伝導帯に励起するのに必要なエネルギーが小さいため、純粋なシリコン結晶中の電子と比べると容易にキャリアとなる。このような半導体は n 型半導体と呼ばれ、添加した 5 価の元素はドナー、ドナーの形成するエネルギー準位はドナー準位と呼ばれる。

図 2.2: アクセプター準位。

図 2.3: ドナー準位。

## 2.3 p-n接合と半導体検出器

p型半導体とn型半導体の接合はp-n接合と呼ばれ、その代表的な利用例はダイオードである。現在の半導体検出器にはこの構造がよく使われているため、以下その説明をする。p型半導体とn型半導体を接合すると、その界面でそれぞれの半導体中の伝導電子や正孔が拡散し、接合部付近ではお互いに結びつく。この結果、接合部付近には空乏層と呼ばれるキャリアが存在しない領域が形成される。またp型半導体は正孔(正の電荷)を失うことになるので相対的に負に帯電し、同様にn型半導体は相対的に正に帯電するため、両者の間には電場が生じることになる。こうしてできた空乏層に荷電粒子が入射して価電子帯の電子にエネルギーを与えると、この電子は伝導帯に遷移し、その後には正孔が出来る。上記の通り空乏層には電場が形成されているので、電子はn型半導体側へ、正孔はp型半導体へそれぞれ引き寄せられていく。空乏層には電荷がないことから再結合が起こらずに、最終的に正孔と電子はp型側、n型側でそれぞれ電気信号として検出できる。一対の電子-正孔対を生成するのに必要なエネルギーはシリコンの場合約3.6 eVであるため、集まった電荷を測定することによって粒子が空乏層内で落としたエネルギーを知ることができる。これが半導体検出器の原理である。

ただしこの原理がうまく機能するためには、空乏層の厚さが十分大きくなければならない。なぜなら、空乏化できていない領域にはキャリアが残っているため、荷電粒子の入射によって生じた電荷がシリコン内を移動している最中に再結合を起こし、信号として検出される電荷量が減少してしまうからである。p-n 接合しただけの状態では空乏層の厚さは数  $\mu m$  程度であり、実用に耐えない。そこで p 型側に比べて n 型側の電位が高くなるように電圧を印加することにより、空乏層を広げるという手段がとられている。ここで印加する電圧を逆バイアス電圧と呼ぶ。半導体検出器を使用する際には逆バイアス電圧を調整することで、検出器全体を空乏化することが理想的である。

## 第3章 計数型SOIピクセル検出器

この章では計数型 SOIPIX 検出器の全体構造およびピクセルの構造、そしてデータの読み出しについて説明する。

## 3.1 計数型 SOI ピクセル検出器の構造

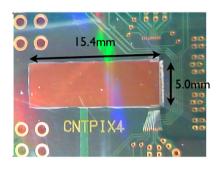

計数型 SOI ピクセル検出器は一定時間内にセンサーに入射した粒子の数を測定するために開発されている SOI 検出器である。この性質の応用例としては X 線の強度測定がある。計数型 SOIPIX 検出器の構造を説明するにあたり、ここでは図3.1 に示す CNTPIX4 と呼ばれる計数型 SOI ピクセル検出器を例にとる。

図 3.1: CNTPIX4。

#### 3.1.1 CNTPIX4の全体構造

${

m CNTPIX4}$  は  ${

m OKI}$  セミコンダクター (株) のデザインルール  $0.2\mu{

m m}$  プロセスによって製造されたチップであり、ピクセル領域とそれを取り巻くように存在する周辺回路から成り立っている。ピクセル領域には  $64\mu{

m m}$  角のチップが  $72\times216$  個 (72列に 216 個ずつ) 実装されている。レイアウト外形は  $5.0{

m mm}\times15.4{

m mm}$  である。

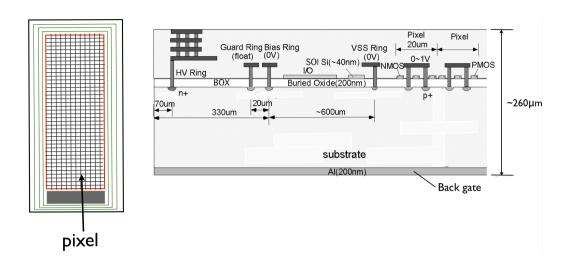

また図 3.2 右に示したように、センサー部分、絶縁層、回路部分を合わせた検出器の厚さは約  $260\mu\mathrm{m}$  となっている。

図 3.2: CNTPIX4 の構造の模式図 (左) と SOIPIX 検出器の断面図 (右)。

#### 3.1.2 CNTPIX4のピクセル構造と動作

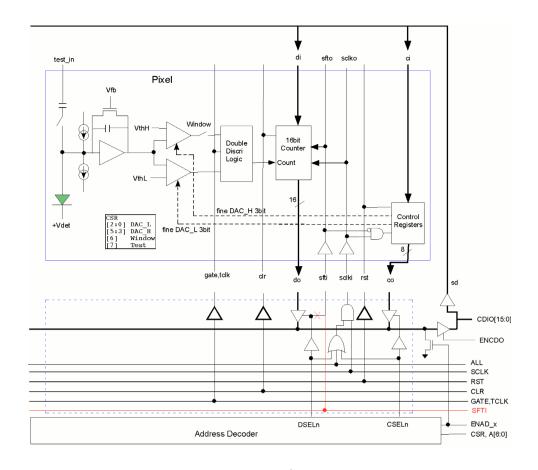

CNPTIX4の各ピクセルは図3.3に示すように、センサー、preamp、discriminator、カウンターなどがら構成されている。discriminatorには2つの閾値があり(VthHとVthL)、preampからの出力パルスの高さが低い方の閾値より大きく、かつ高い方の閾値より小さい場合のみデジタルパルスが出力され、このデジタルパルスを認識したカウンターがカウント値を1つ増やすという仕組みになっている。カウンターのダイナミックレンジは16bitである。なお電圧が高い方の閾値を機能させず、電圧が低い方の閾値のみで動作させることも可能である(本研究での全ての測定はこちらで行っている)。この動作が計数型と呼ばれている所以である。

#### 3.1.3 Control Register

図 3.3 にある Control Register (以下 CSR) は、計数型 SOIPIX 検出器の各ピクセルに実装されている register で、8bit の情報を保持できる。CSR に書き込む 8bit の情報には次のような意味がある。

#### (1) 閾値の補正

CNTPIX4の閾値は全ピクセルに対して同じ値を設定するようになっているが、CSR に書き込んだデータを使うことで、ピクセルの個体差に応じて閾値を補正することができる。閾値1つにつき補正用に3bit が割り当てられているため、CNTPIX4ではピクセルごとに6bit が割り当てられている。

図 3.3: CNTPIX4 の各ピクセルの概略図。

#### (2) 使用する閾値の数の選択

CNTPIX4 は高い方の閾値を機能しないようにして動作させることができる。 高い方の閾値を機能させる/機能させないの選択のために1bit が割り当てられている。

#### (3) テストパルスの入射のためのスイッチ

${

m CNTPIX4}$  には回路の動作確認のためにテストパルス (疑似信号) を入力する機能がある。テストパルスを入力するための端子は図 3.3 で  ${

m test\_in}$  と表されている端子である。テストパルス入力の  ${

m on/off}$  のために  $1{

m bit}$  が割り当てられている。

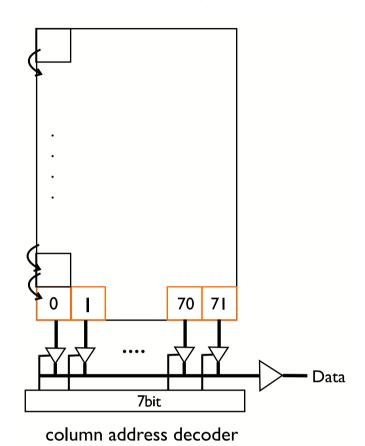

## 3.2 カウンター値の読み出し

CNTPIX4 では各ピクセルの column address(以下 CA) の指定は 7bit のアドレスをチップ外部から指定することで行う。図 3.4 中で赤い四角で囲んだ値が column

address である。7bit の情報が指定されると column address decoder により指定された CA が選択される仕組みになっている。

図 3.4: CNTPIX4の column addressの指定。

ここでは各ピクセルのカウンター値の読み出しについて説明する。図 3.4 に示したように、一番下の行のピクセルは column address decoder に接続されており、CA を指定すると対応したピクセル内のカウンター値がデータとして出力できるようになる。各ピクセルのカウンターは自身の上下にあるピクセルのカウンターと回路的につながっており、CA を指定したうえでシフト信号を送ると、指定した列の下から 2 番目のピクセルのカウンターの値が一番下のピクセルへ、一番下のピクセルのカウンターの値は一番上へ… というように、列内でカウンター値を下に移動させることができる。CA0 を選択してシフト信号を送った場合のデータの移動を図 3.4 に示している。一番下のピクセルのカウンター値の読み出し、データのシフト… という動作を 216 回繰り返せば、一列全てピクセルのカウンター値を読み出せる。これに加えて、72 個ある CA を次々に指定して、全てのピクセルのカウンター値を取得する。

## 第4章 計数型SOIPIX検出器のアナ ログ特性

この章では計数型 SOIPIX 検出器のアナログ特性の評価結果について報告する。

### 4.1 測定対象と用いた検出器

測定に用いた計数型 SOIPIX 検出器は CNTPIX4 と CPIXTEG1 と呼ばれるものである。CPIXTEG1 は計数型 SOIPIX 検出器の一つで、レイアウト外形は 2.5 mm 角であり、 $64~\mu\text{m}$  のピクセルが  $32 \times 32$  個実装されている。

センサー部分のダイオード特性を CNTPIX4 を用いて、また preamp の gain の 測定を CPIXTEG1 を用いて行った。なお CPIXTEG1 の preamp には、センサー上に配置されているもの (ピクセル内の読み出し回路の一部としての preamp) と、単独で実装されているもの (preamp 単体の動作確認用でセンサーがついていない)の 2 種類があり、本研究の測定では全てセンサー上の preamp を用いた。

## 4.2 センサー部分のダイオードの I-V 特性

${

m CNTPIX4}$  のセンサー部分に逆バイアス電圧 (以下  $V_{back}$ ) をかけて、ダイオードの I-V 特性を測定した。測定には KEITHLAY 社の  ${

m SourceMeter}2612A$  を使用した。

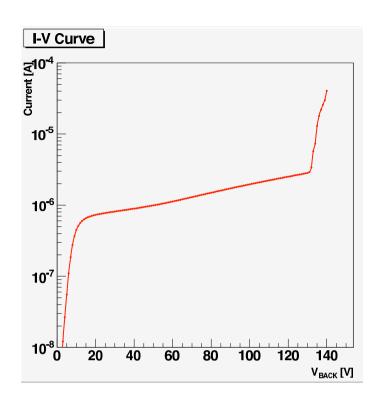

結果を図 4.1 に示す。これを見ると良好なダイオード特性を示していることが分かる。ブレイクダウンはおよそ 130V で現れているが、全空乏化には約 300V が必要であり [2]、この段階ではまだ全空乏化には至っていない。

センサーの有効体積を増やし検出効率を上げるためにも、空乏層を厚くすることが重要である。全空乏化のためには、比抵抗値の高い基板の使用、またはブレイクダウン電圧が現在よりも高くなるような設計、が必要である。

図 4.1: センサー部分のダイオードの I-V 特性

## 4.3 アナログ回路のパラメータの調整

ここではアナログ回路のパラメータの調整について述べる。CPIXTEG1を動作させる際に調整が必要なパラメータのうち、本研究で重点的に取り扱ったのは次の二つである。

- ・VREF\_AMP preamp からの出力のベースラインを決める参照電圧

- ・VREF\_SHP shaper からの出力のベースラインを決める参照電圧

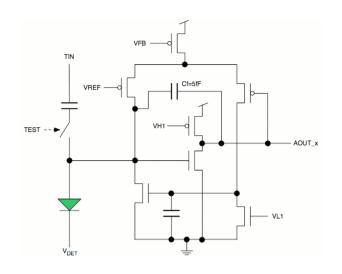

以降では $VREF\_AMP$  と $VREF\_SHP$  をまとめて「2 つのVREF」と呼ぶことにする。図 4.2 は preamp の回路図で、 $VREF\_AMP$  は図中の「VREF」で示した位置である。

#### 4.3.1 2つの VREF の調整

2 つの VREF の値を変化させながらテストパルスに対する preamp の応答を調べた。テストパルスに対する preamp の反応は次の 3 通りに分類した。

図 4.2: preamp の回路図

#### ・期待される反応

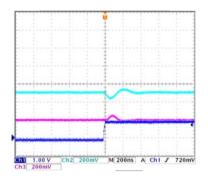

図 4.3 のようにテストパルスの変化 (エッジ) に反応して、preamp の出力波形が変化している。preamp の出力としてはこのような波形が期待されている。「期待される反応」をしていると判断する条件は、テストパルス入射後  $1\mu s$  以内に波高  $100 \mathrm{mV}$  以上の出力波が存在することである。

#### ・発振

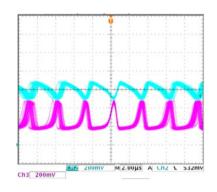

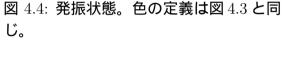

図4.4のようにテストパルスを入力したかどうかに関わらず、信号が出力されている状態。出力波形が周期的である場合には「発振」していると判断する。

#### ・反応無し

図4.5のようにテストパルスを入射しても「期待される反応」で見たようなパルスが preamp から出力されていない。「反応無し」と判断する条件は「期待される反応」も「発振」もしていない、である。

性能評価を進めるにあたっては上の3つのうち preamp が「期待される反応」をする領域で実験をする必要があるため、ここでは2つの VREF の値を変化させながら、その条件での preamp の応答が上の3つのうちどれに分類できるかを調べた。結果は図4.6の通りで、

・VREF\_AMP が 0.8V 以上になるとテストパルスに反応せず、かつ発振も起こらない

図 4.3: テストパルスに対して反応している状態。テストパルスは濃い青、preampの出力は水色である。

図 4.5: テストパルスに対して反応してい ない状態。色の定義は図 4.3 と同じ。

・VREF\_AMPが0.7V以下の場合にはテストパルスには反応しているが、VREF\_SHPの値によっては発振が起こる

ということが分かる。本研究では2つの VREF の値が「期待される反応」の範囲に収まるように、 $VREF\_AMP=0.57V$ 、 $VREF\_SHP=0.50V$  に設定した。

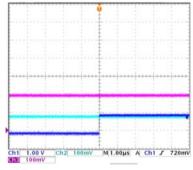

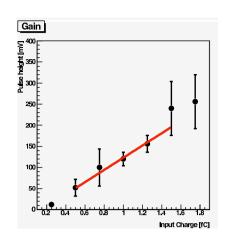

### 4.4 Gain 測定

$\operatorname{preamp}$  の  $\operatorname{gain}$  を測定するためにテストパルスを  $\operatorname{preamp}$  に入射し、出力の波高をオシロスコープで測定した。入射する電荷量を変えて同様の測定を繰り返した結果を図 4.7 に示す。測定点を直線で  $\operatorname{fit}$  し、その傾きから  $\operatorname{gain}=(262\pm47)\operatorname{mV/fC}$  と求めた。この値は設計値である  $142\operatorname{mV/fC}$  と比較すると有為に大きな値になっている。なお図の一番右の点を  $\operatorname{fit}$  の対象から外した理由は、入力する電荷量をこれ以上増やしても出力の波高が高くならなかったことから、  $\operatorname{preamp}$  の出力が飽和したと判断したためである。なお、結果的に入力電荷が  $\operatorname{1fC}$  の段階で  $\operatorname{preamp}$  の出

○:テストパルスに反応、かつ発振無し △:テストパルスに反応せず、かつ発振無し

□: テストパルスに反応、かつ発振有り

0.90  $\triangle$ 0.80  $\triangle$ Δ Δ Δ Δ Δ  $\triangle$  $\triangle$ VREF(preamp) 0.70  $\bigcirc$  $\bigcirc$  $\bigcirc$ [V] 0.60  $\bigcirc$  $\bigcirc$  $\bigcirc$ 0.50  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$  $\bigcirc$ 0.70 0.50 0.60 0.80 0.90 1.00 1.10 1.20 1.30

VREF(shaper) [V]

図 4.6: 2 つの VREF の値と preamp の反応

力が飽和していることになるが、設計上は入力電荷が1.6fCまでは入力電荷と出力 の波高の間に線形性が求められる。設計値と今回の実験結果の食い違いの原因に ついては検証が必要である。

$\boxtimes$  4.7: preamp  $\mathcal{O}$  gain

## 第5章 動作試験

計数型 SOIPIX 検出器については、これまでに可視光および X 線に対する反応が確認されたものの、定量的な評価はなされていない。そこで、今後の計数型 SOIPIX 検出器開発に対する指針をあたえるべく、より定量的な測定を試みた。本章ではその結果について述べる。

また計数型 SOI 検出器の出力である「計数」を取得するシステムについてもここで簡単に説明する。

## 5.1 DAQシステムの開発

#### 5.1.1 読み出し用汎用ボード: SEABAS

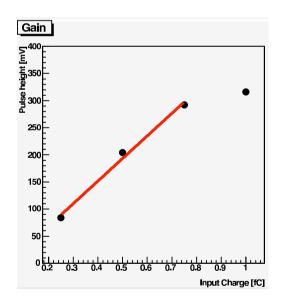

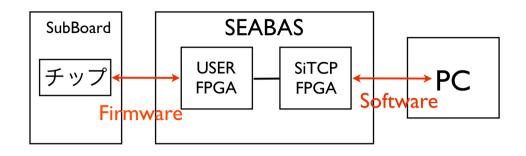

SOIPIX 開発グループでは、SOI ピクセル検出器の種類に関係なく共通の方法でチップのテストをするために、図5.1 に示す Soipix EvAluation BoArd with SiTCP (SEABAS) と呼ばれる汎用ボード用いている。SEABAS には SiTCP と呼ばれるネットワークプロセッサが搭載されているため、Ethernet 経由で DAQ を行える点が大きな特徴である。Ethernet 経由でのやりとりは SITCP FPGA と呼ばれる FPGA で制御されている。また、チップとの信号のやりとりは USER FPGA と呼ばれる FPGA を使って行っている。信号処理の内容は Verilog HDL と呼ばれるプログラミング言語で記述できるようになっている。SOI 検出器はその種類が変わると処理するべき信号も変わってしまうが、この違いの大部分は FPGA で行う処理で吸収できるので、SOI 検出器の種類によらず SEABAS 経由で DAQ 可能である。

以下で述べる一連の試験でも DAQ は全て SEABAS 経由で行っている。

#### 5.1.2 SubBoard

SEABAS を用いた DAQ では FPGA により信号処理を行うが、検出器単体では SEABAS と接続することができない。そこで SEABAS と検出器の間で信号のやり

☑ 5.1: SEABAS

取りを可能にするために、検出器ごとに SubBoard を用意する。図 5.2 は CNTPIX4 の SubBoard である。CNTPIX4 のチップは SubBoard にワイヤボンディングされている。一方、図 5.3 に示すようなパッケージに実装された状態のチップもある。パッケージに実装されたチップの場合には、パッケージを差し込むためのソケットが実装された SubBoard を使う。

☑ 5.2: CNTPIX4 SubBoard

図 5.3: パッケージに実装された状態の チップ。

### 5.1.3 DAQ の流れ

SEABAS を用いた DAQ の大まかな流れは次の通りである。DAQ の概略を図 5.4 に示す。まず PC から SEABAS 上の SiTCP FPGA に TCP 接続確立の要求を送る。TCP 接続を確立した後、DAQ 開始の合図や DAQ に必要なパラメータを SiTCP FPGA を通して USER FPGA に送る。ここでいうパラメータとは discriminator の 閾値や計数時間である。

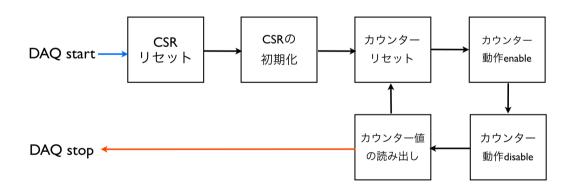

DAQ 開始の合図を受け取ると、USER FPGA は Verilog HDL で記述された順序に従ってチップをコントロールする。図 5.5 にあるように、CSR のリセットと

図 5.4: DAQ システム

CSR の初期化の後、カウンターリセット、カウンター動作 enable、カウンター動作 disable、カウンター値読み出しを行い、再びカウンターリセット、カウンター動作… と繰り返す。

DAQ を終了させる場合には DAQ 開始時と同様に、PC から DAQ 終了の合図を USER FPGA に送る。DAQ 終了の合図を USER FPGA が受け取ると、図 5.5 に おけるループから抜け出し、USER FPGA は DAQ 開始前の状態に戻る。DAQ 終了後は TCP 接続を閉じる。ここまでが DAQ の流れである。

以降説明の簡略化のために、図 5.5 においてカウンターリセットからカウンター 値読み出しまでを繰り返した回数を「イベント数」と定義する。

図 5.5: DAQ の流れ

## 5.1.4 DAQ用プログラム

SEABAS を用いた DAQ では、図 5.4 にあるようにチップを動かすために必要な FPGA の動作を記述したプログラムと、検出器からのデータを PC で受け取るために必要な Software (本研究では C++で記述されたもの) の二つが必要である。これらのプログラムに関しては積分型 Pixel 検出器の性能評価の際に廣瀬穣氏が作成したもの [2] があるため、計数型検出器に対応できるように変更を加えた上で使用している。

### 5.2 カウンターの動作テスト

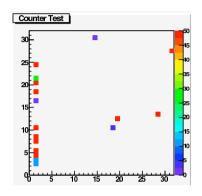

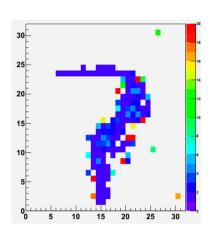

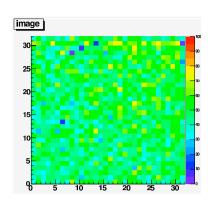

カウンターの動作テストとして、ここでは指定した回数だけテストパルスを全ピクセルの preamp に入力した後、カウンターの値を読み出し、カウンターの値が入力回数と一致するか確認した。検証方法は、テストパルスを 90 回入力する  $\rightarrow$  カウンターの値を読み出す、という操作を合計 50 回繰り返し (50 イベント分のデータを取得)、出力値が 90 (=テストパルス入力回数) にならなかった回数の合計を各ピクセルについて計算した。結果は図 5.6 の通りである。

図 5.6: 各ピクセルが 90 を出力しなかった回数。

図 5.6 に示すように、色のついているピクセルは 17 個 (全ピクセルの 1.7%) であり、全体の 98%以上のピクセルは 50 イベント全てで 90 を出力していることが分かる。一方、色のついている 17 個のピクセルの中には、50 回のうち 1 回も 90 を出力しなかったピクセルもある。カウンターの値を用いた解析を行う際にはこのようなピクセルがあることに注意する必要がある。

## 5.3 可視光に対する応答

${

m CPIXTEG1}$  に可視光を照射し、その応答を確認した。可視光源は波長は  $635{

m nm}$  の LED の光であり、検出器と LED の距離を 1 から  $2{

m cm}$  に保った状態で測定を行った。測定中は測定計全体をブラックシートで覆い、検出器に LED 以外の光が入射しないようにしている。主な動作パラメータは以下の通りである。 $V_{back}=90.0V$ 、1 イベントごとの計数時間= $100{

m ms}$ 、閾値= $500{

m mV}$  である。

この条件の下で CPIXTEG1 に対して図 5.7 で示すマスク (真鍮製) ごしに LED を照射した。結果は図 5.8 の通りである。なおこの実験では検出面の大きさの都合で、マスクにある文字のうち「7」のみを映すようにしている。図 5.8 を見るとマスク通りのイメージが取得できたので、CPIXTEG1 が可視光に反応していることが確認できた。

また 5.1.4 で触れたように、本実験で用いた DAQ プログラムは既存のプログラムを CPIXTEG1 の試験用に変更したものであるため、プログラムの動作テストも兼ねている。この点についてもマスクのイメージの取得ができたことから、信号読み出しが正常に行えていることが分かる。

図 5.7: 実験に用いたマスク。

図 5.8: CPIXTEG1 にマスク越しに LED を照射した画像。

## 5.4 X線に対する応答

${

m CPIXTEG1}$  に  ${

m X}$  線を照射し、その応答を確認した。本実験では加速した電子を  ${

m Mo}$  ターゲットに衝突させることで発生する  ${

m X}$  線を使用している。また銀フォイルを用いて低エネルギーの  ${

m X}$  線 (主に連続  ${

m X}$  線) をカットしているため、 $17.4{

m keV}$  が主成分となっている。この実験で用いた  ${

m X}$  線発生装置はリガクの  ${

m SA-HFM3}$  である。

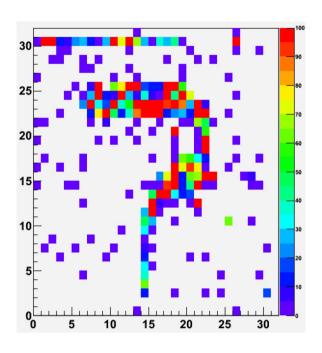

#### 5.4.1 X線に対する応答の確認

5.4 節で用いたものと同じ真鍮製のマスクを使って X 線に対する反応を確認した。 X 線の照射口から検出器までの距離は約  $50 \, \mathrm{cm}$  で、 X 線が検出器の回路側からセンサー側に進むように検出器を設置している。また X 線スポットの大きさは、CPIXTEG1 全体に X 線があたる程度に大きくしてある。結果は図 5.9 である。 Y ズが多いながらも、可視光のときと同様に Y の文字が見えることから、CPIXTEG1 が X 線にも反応していることが分かる。

図 5.9: CPIXTEG1 にマスク越しに X 線を照射した画像。

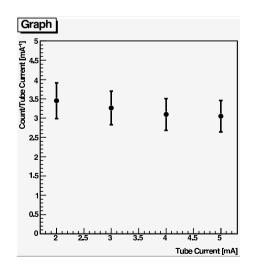

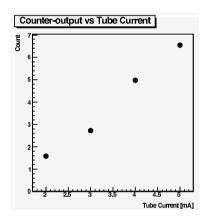

#### 5.4.2 X 線の強度とカウンター出力

計数型検出器の重要な応用はX線などの強度測定である。そこでカウンター出力のX線強度に対する線形性を調べた。X線発生装置の管電流を変化させ、各管電流値における出力の平均値を図示したのが図5.10である。各点は20イベントに対する全ピクセルからの出力の合計を測定時の管電流の値で割ったものである。

なお本測定ではカウンターをリセットできなくなる現象  $(5.7.2 \, \pm 2.0)$  の影響を軽減するために、1 イベントあたりの計数時間を  $10 \, \mathrm{ms}$  にしてある。

図 5.10: カウンター出力の管電流依存性。縦軸はカウンター出力を管電流の値の比である。

図 5.10 を見ると、カウンター出力と管電流の値は比例していることが分かる。管電流の値は X 線の強度に比例するため、この結果はカウンター出力が X 線の強度に比例していることを意味している。

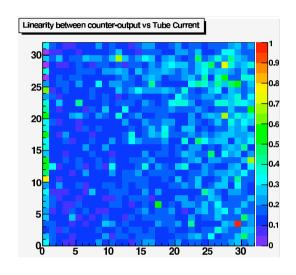

次に各ピクセルごとに線形性がどの程度成り立っているかを調べた。方法は図5.10のプロットを各ピクセルについて作成し (図5.10は全ピクセルからの出力の合計のプロットである)、これを y=C (定数) という直線で fit したあと、fit で求めた C でその誤差  $\delta C$  を割った値をヒストグラムにした。結果は図5.11 である。図5.11 を見るとカウンター出力と管電流の間の線形性はピクセル間でばらついていることが分かる。

図 5.11: 各ピクセルの出力と管電流の間の線形性。

## 5.5 X線照射前後での性能の変化

### 5.5.1 X線照射とpreampのgain

管電圧を 25kV、管電流を 10mA に設定して X 線を約 10 分照射した後、4.4 節で説明した測定方法および測定条件で preamp の gain を測定したところ  $(145\pm35)$ mV/fC となった (図 5.12)。この値は照射前の  $(262\pm47)$ mV/fC の約 55%となっている。gain が小さくなったためか、照射前には飽和していた 1fC の電荷を入力しても preamp の出力は飽和しなかった。gain が小さくなる理由は現時点では分かっていない。

図 5.12: X 線照射後の preamp の gain。

#### 5.5.2 X 線照射に伴う残像

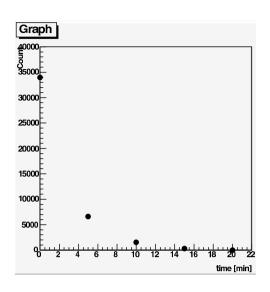

計数型 SOIPixel 検出器に X 線を照射し続けると、カウンターの値をリセットできない (=0 に戻すことができない) という現象が確認されている。同時に、検出器に紫外線を照射するとカウンターの値をリセットできる、あるいは 0 には戻らないものの紫外線照射前に比べて値が 0 に近付くことが報告されている。そこで、CPIXTEG1 でも同様の現象を観測できるか実験を行った。管電圧を  $25 \mathrm{kV}$ 、管電流を  $10 \mathrm{mA}$  に設定して X 線を約 10 分間照射し、カウンターがリセットできない状態にした後、紫外線を照射しながら 5 分ごとに全ピクセルからの出力の平均を計算した。

結果は図 5.13 に示す。X 線を照射した直後の測定ではカウンターの値が大きいが、(カウンター出力の最大値は 65535)、20 分ほど紫外線を照射することによりカウンターの値が 0 に戻った。このことから、カウンターがリセットできないピクセルを持つ計数型 SOIPIX 検出器に紫外線を照射すると、カウンターがリセットできないピクセルが減少すること、また照射時間が長いほど減少量が多いことが分かった。

## 5.6 放射線源に対する応答

ここでは  $\beta$  線に対する応答について述べる。検証方法は放 Cd(109) 射線源を検出器の前に置いた場合と置かなかった場合でそれぞれ 10 分ほどデータ取得を行うというものである。discriminator の閾値は 500 mV、1 イベントあたりの計数時間は 100 ms とした。また、Cd 放射線源から放出される  $\beta$  線のエネルギーは表 5.2 の通りである。

10 分間の各ピクセルからの出力の合計を示したのが図 5.14 と図 5.15 であり、両

図 5.13: カウンター出力の紫外線照射による回復。

者の間にははっきりとした違いがあることが分かる。実際には今回放射線源として用いた  $\mathrm{Cd}(109)$  からは  $\gamma$  線  $(0.088\mathrm{MeV},\mathrm{probability}:3.6\%)$  も出ているが、いずれにせよ検出器が  $\beta$  線か  $\gamma$  線に反応していることが確認できる。

エネルギー [MeV]

放出確率 [%]

0.063

41

0.084

45

0.087

9

表 5.2: Cd から放出される  $\beta$  線のエネルギーと放出確率

## 5.7 Back gate effect

### 5.7.1 Back gate effect ∠ BPW

SOI 検出器に特有の問題の一つに Back gate effect がある。これはセンサー部に 逆バイアスをかけることによって生じた電場が回路部のトランジスタの動作に影響を与えることによって起こる現象で、場合によってはトランジスタが動作しなくなってしまう。SOIPIX グループでもこの現象を確認しており、SOI 検出器の実用化のためには Back gate effect の解消は大きな課題の一つとなっている。

Back gate effect の対策として現在 SOI グループで採用されているものは、センサー領域と酸化膜の境界付近に高濃度のアクセプターを含む層をインプラントするという方法である。このインプラントされた層は Buried P-Well (以下 BPW) と

図 5.15: 放射線源を用いた場合。

呼ばれている。この BPW 層の電位を GND に固定することにより、トランジスタの電位がバイアス電圧によって変化することを防ぐというアイデアであり、少なくとも積分型 SOIPIX 検出器については SOIPIX グループの測定でその効果が確認されている。

#### 5.7.2 計数型 SOI 検出器における BPW の効果

BPW の効果を検証するために、BPW が実装された計数型 SOI 検出器と実装されていない計数型 SOI 検出器で X 線に対する応答を比較する。前節までの測定に使った CPIXTEG1 には BPW が実装されているため、ここでは BPW が実装されていない検出器に関する結果を述べる。

BPW が実装されていない検出器としては CNTPIX3 と呼ばれる計数型 SOI 検出器の中の BPW が実装されていないピクセルのみを測定対象とした。

測定内容はカウンター出力の管電流依存性とカウンター出力の $V_{back}$  依存性である。ここで、カウンター出力は 20 イベント分の全ピクセルの出力の平均値と定義した。図 5.16 に  $V_{back}$  が 0.7V の時のカウンター出力の管電流依存性を、図 5.17 に管電流が 2mA の時のカウンター出力の  $V_{back}$  依存性をそれぞれ示した。いずれも discriminator の閾値は 800mV に設定している。

図 5.16 から、 $V_{back}$  が小さい場合には X 線に対するピクセルの反応は良好ということが分かる。一方、図 5.17 から分かるように、BPW が無い場合には  $V_{back}$  が 1.0V 程度で出力が 0 になっており、検出器が X 線に応答していない。 $V_{back}$  の上昇に伴って回路が正常に動作しなくなる Back gate effect の典型例である。BPW がある場合には観測しなかった現象であることから、BPW には Back gate effect を抑制する効果があることが分かる。

図 5.16: BPW 未実装のピクセルの出力の 図 5.17: カウンター出力の  $V_{back}$  依存性。

## 第6章 まとめと考察

この章ではここまでの結果の整理と今後の開発方針についての考察を述べる。

### 6.1 アナログ回路

アナログ回路の試験で確認できたことは、センサー部のダイオード特性、アナログ回路のパラメータ調整、および preamp の gain の測定である。

センサー部のダイオード特性はCNTPIX4を用いて測定を行い、良好なダイオード特性を示していることが確認出来た。なお、ダイオード特性の測定結果からブレイクダウン電圧が約130Vであることが分かるが、130Vではセンサー部の全空乏化はできないため、使用する基板または設計での工夫が必要となる。

アナログ回路のパラメータ調整では、CPIXTEG1の preamp が 2 つの VREF の値によって、テストパルスに反応し、かつ発振が起こらないようにできることを確認した。4.1 で述べたように preamp は CPIXTEG1のセンサー上の preamp である。一方、2 つの VREF の値によっては preamp で発振が起こることが確認された。原因はまだ解明出来ていないが、センサーのついていない preamp では発振を観測していないことから、センサーとの間のカップリングが発振の原因になっている可能性は高い。

preampの gain に関しては、preampへの入力電荷が 1fC 未満の時に  $gain=(262\pm49)$  mV/fC という結果を得た。preamp が動作していることは確認できたが、gain が設計値よりも有為に大きな値をとっている。設計値との食い違いの原因については検証が必要である。

### 6.2 動作試験

動作試験ではカウンターの動作テスト、および可視光、X 線、 $\beta$  線に対する CPIX-TEG1 の反応を確認した。

カウンターの動作テストでは、全体の 98%以上のピクセルのカウンターが、テ

ストパルス入力回数と同じ値を出力していることを確認した。一方でテストパルス入力回数と出力が1回も一致しなかったピクセルもあり、解析の際にはこのようなピクセルの扱いに注意する必要がある。 X線照射実験では真鍮製マスクのイメージが取得でき、X線に対して反応していることが確認できた。またカウンター出力と管電流の値の間の線形性が確認できたが、線形性がピクセル間でばらついていることも分かった。更にX線照射前後でpreampのgainが変化していることが明らかになった。

$\beta$  線源を用いた測定では線源として  $\mathrm{Cd}(109)$  を使用し、線源を検出器の前に置いた場合と置かなかった場合でカウンター出力を比較した。その結果、両者の間には有為な差があり、 $\mathrm{CPIXTEG1}$  が線源に対して反応していることが確認できた。なお、 $\mathrm{Cd}(109)$  からは  $\gamma$  線も出ているため、この結果のみでは  $\mathrm{CPIXTEG1}$  が  $\beta$  に反応したとは結論づけられないが、 $\mathrm{CPIXTEG1}$  が  $\beta$  線か  $\gamma$  線に反応していることは確実である。

### 6.3 BPW について

$V_{back}$  が高いほど空乏層が厚くなるため、検出器としての実用化という観点からは高い $V_{back}$  をかけられることが望ましい。 $\mathrm{SOI}$  検出器の場合には $V_{back}$  を高くすると Back gate effect を避けて通れないが、 $\mathrm{BPW}$  によって Back gate effect の影響を抑制できることが分かっている。本研究でも 5.9.2 で述べたように、計数型  $\mathrm{SOIPIX}$  検出器における  $\mathrm{BPW}$  の効果を確認できた。

実用化を考慮すると、全空乏化のために  $V_{back}$  が  $200\mathrm{V}$  から  $300\mathrm{V}$  という高い状態で使用することが予想できるため、 $V_{back}$  が更に高い状態での BPW の効果の検証を行うことが今後の課題である。

### 6.4 X線照射に伴うカウンターの異状について

5.6.4 で述べたように X 線を長時間照射し続けると、計数型 SOI 検出器のカウンターがリセットできなくなる。現時点ではこの現象の原因は次のように考えられている。

X線が酸化層を通って検出器に入射すると、センサー領域のみではなく酸化層でも電子ー正孔対が生成される。この電子ー正孔対はエネルギー的に酸化層にトラップされてしまうため、入射する X線が多いほど蓄積される電子ー正孔対が多くなる。蓄積された電子と正孔のうち、電子は束縛エネルギーはあまり大きくないため酸化層からすぐに抜け出し、酸化層には正孔が残る。すると酸化層の電位が変化し、トランジスタとの間で Back gate effect が引き起こされてしまうため、

場合によってはトランジスタが動作しなくなる。カウンターがカウント数を保持できるのは、カウンターが flip flop で構成されているためであるが、flip flop を構成するトランジスタが動作しなくなれば、リセットできないように見えるはずである。この考え方に基づくと、この現象そのものは X 線に限らず粒子線を照射した場合にも起こりうることになる。

カウンターがリセットできない理由を酸化層に正孔がトラップされているためと仮定すると、これを解決するには電荷にエネルギーを与えて束縛状態から解放すればよい。このエネルギーを与える手段としてグループ内で現在採用されているものが紫外線照射である。また紫外線照射以外の手法の候補としては加熱があり、その効果は現在検証中である。

## 第7章 結論

本研究では計数型 SOIPIX 検出器の性能評価を行い、センサー部が良好なダイオード特性を示すことや可視光、X 線などに反応していることなど、ポジティブな結果を得た。

一方で、preamp の gain の測定値が設計値より大きいこと、preamp とセンサー部の coupling により発振が起こることが判明した。また X 線や放射線源に対する計数型 SOIPIX 検出器の反応に関する定量的な考察がまだ不足している。以上が本研究から見た SOIPIX 検出器開発における課題である。

## 謝辞

はじめに、今回の実験を行う環境を与えて下さり、また折に触れて高い視点から助言を下さるなど、私の研究を見守って頂いた山中卓教授に深くお礼申し上げます。

指導教官である花垣和則准教授には、SOIPIX 検出器の開発に携わる機会を与えて頂いただけでなく、研究に対する姿勢を時に厳しく時に優しく指導して頂きました。感謝しています。

助教の外川学さんからは、折に触れてシリコンに関する一般的な知識を頂きま した。ありがとうございました。

秘書の亀井彰子さんには、私が長期間 KEK で研究を進めていたこともあり、事務関係で様々なサポートをして頂きました。お世話になりました。

KEK の新井康夫さん、三好敏喜さんをはじめ SOIPIX 開発グループの皆様には、お忙しい中丁寧なご指導を頂きました。この分野に関しては素人だった私がこの研究を進められたのは皆様のおかげです。感謝致します。

山中研究室在学中の廣瀬穣さんには、過去に SOIPIX 検出器を研究した先輩として、参考になる意見を頂きました。ありがとうございました。また特任研究員の李栄篤さん、ならびに山中研究室在学中の先輩である岩井瑛人さん、佐藤和史さん、廣瀬穣さん、目黒立真さん、李宗垣さん、村山恵理さんには、中谷洋一さん、柳田陽子さんからは、ことあるごとに多くの知識を頂きました。特にコンピュータに詳しくない私にとっては、コンピュータに関する話は勉強になりました。後輩の宇井利昌君、遠藤理樹君、浅川直也君、鎌倉恵太君、伴野真太郎君、東野聡君、研究生の TEOH Jia Jian 君には、他愛も無い話に付き合ってもらい、楽しい時間を過ごすことができました。ありがとうございました。同期の岡村航君、杉山泰之君とは研究とはあまり関係ない話でよく盛り上がっていたように思います。二人とは違う道を進むことになりますが、お互いに頑張りましょう。そしてありがとう。

皆様のおかげで、無事実験結果をまとめることが出来ました。 本当にありがと うございました。

## 参考文献

- [1] S. M. Sze, 「SEMICONDUCTOR DEVICE Physics and Technology 2nd Edition」 John Wiley & Sons Inc(2001)。

- [2] 廣瀬穣 修士論文「SOI 技術を用いた一体型 Pixel 検出器用読み出しシステム の開発、及び積分型 Pixel 検出器の性能評価 」 大阪大学 (2009)。